ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

5.4 PostOffice Handshaking Protocol

Reading data from or writing data to any of the ZR36067 guests

using the PostOffice mechanism requires the host software to

follow the handshaking protocol described below. The main idea

is that the host has to poll the PostOffice request pending bit in

order to confirm the availability of the GuestBus and verify the

validity of the data contained in the PostOffice data byte. In

general, host accesses to the PostOffice register may change

the PostOffice pending bit, as explained below. Thus, the host

software must ensure that accesses to the PostOffice register

are governed by a central routine. For example, independent

accesses to the PostOffice register both from an interrupt

service routine and the main processor task(s), or from more

than one task in a multitasking environment, might cause a

deadlock, unless explicit protection measures are taken.

5.4.1 Host Writes to a Guest Device

• The host reads the PostOffice register, and checks the Post-

Office pending bit. If this bit is ‘1’, the write cycle cannot be

executed now, because the GuestBus master is busy exe-

cuting a previous PostOffice read or write request. Once this

bit is ‘0’, the write request can be made.

• The host writes a full doubleword to the PostOffice register,

containing the data byte to be sent to the guest, the guest’s

identity (0,...,7), the specific guest register (0,...,7), and an

indication that this is a write request (direction bit = 1). As a

result of writing to the PostOffice data byte, the PostOffice

pending bit is set to ‘1’.

• The ZR36067 completes the current code-write cycle, if one

is being executed, and, before executing the next code-write

cycle (if one is needed), it executes the pending PostOffice

request. At the completion of the GuestBus write cycle it

clears the request pending bit.

• The host may read the PostOffice register, to verify that the

pending bit is ‘0’, meaning that the write request has been

completed.

• Note that in multiple (back-to-back) PostOffice operations

the host has to poll the request pending bit only once be-

tween two requests, since reading this bit zero indicates

both that the previous request has been completed and that

the next request can be made.

5.4.2 Host Reads from a Guest Device

• The host reads the PostOffice register, and checks the Post-

Office pending bit. If this bit is ‘1’, the read cycle cannot be

executed now, because the GuestBus master is busy exe-

cuting a previous PostOffice read or write request. Once this

bit is ‘0’, the read request can be made.

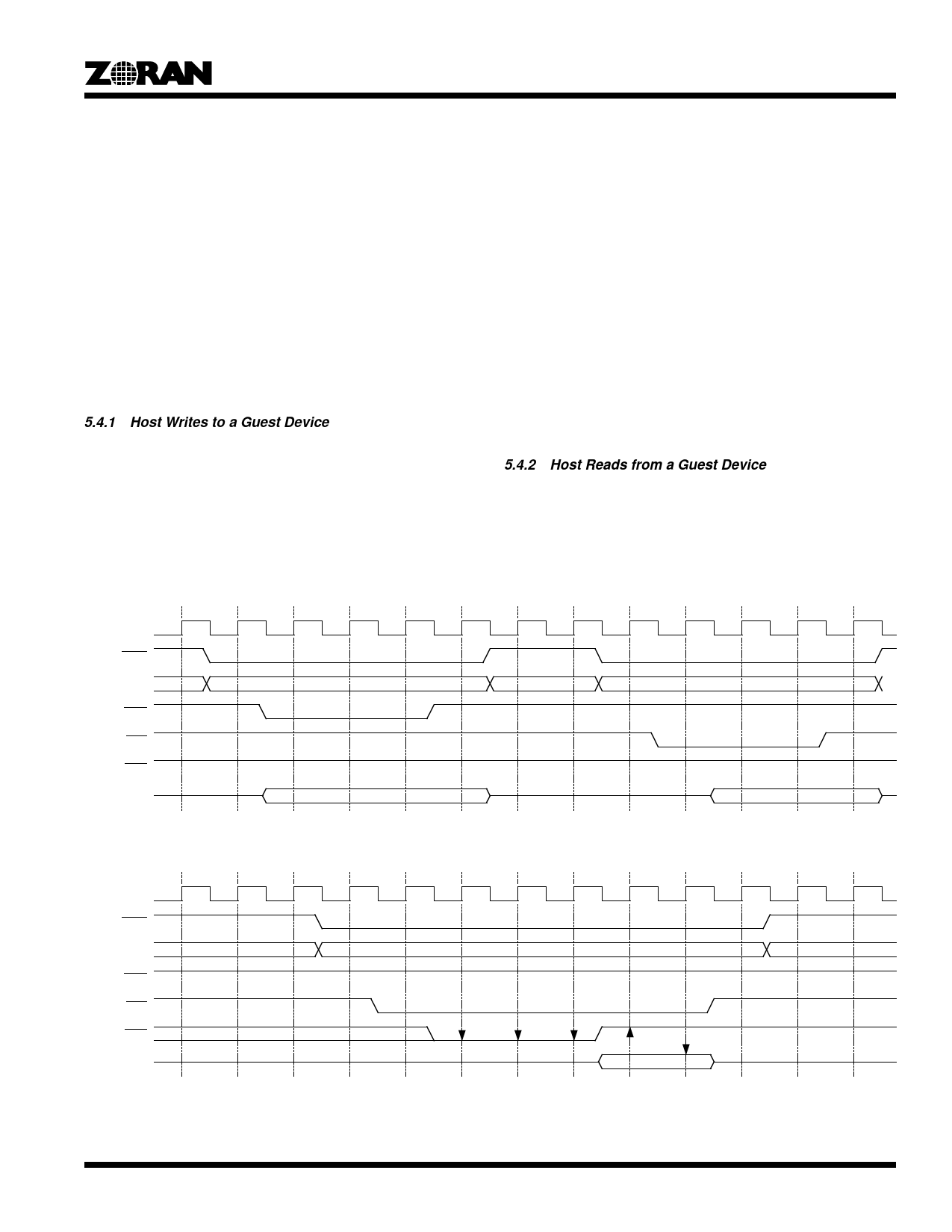

PCI CLK

GCS0

GADR[2:0]

GWR

GRD

GWS

GDAT[7:0]

1

2

3

4

5

6

7

8

9

10

11

12

13

0x0

0x5

Data valid from ZR36067

Example 1

Data valid from Guest

PCI CLK

GCS2

GADR[2:0]

GWR

GRD

GWS

GDAT[7:0]

1

2

3

4

5

6

7

8

9

10

11

12

13

0x1

Sampling Points

Example 2

Figure 4. Two Examples of GuestBus Cycles

15