VT82C596 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

VT82C596 Datasheet PDF : 96 Pages

| |||

:H &RQQHFW 7HFKQRORJLHV ,QF

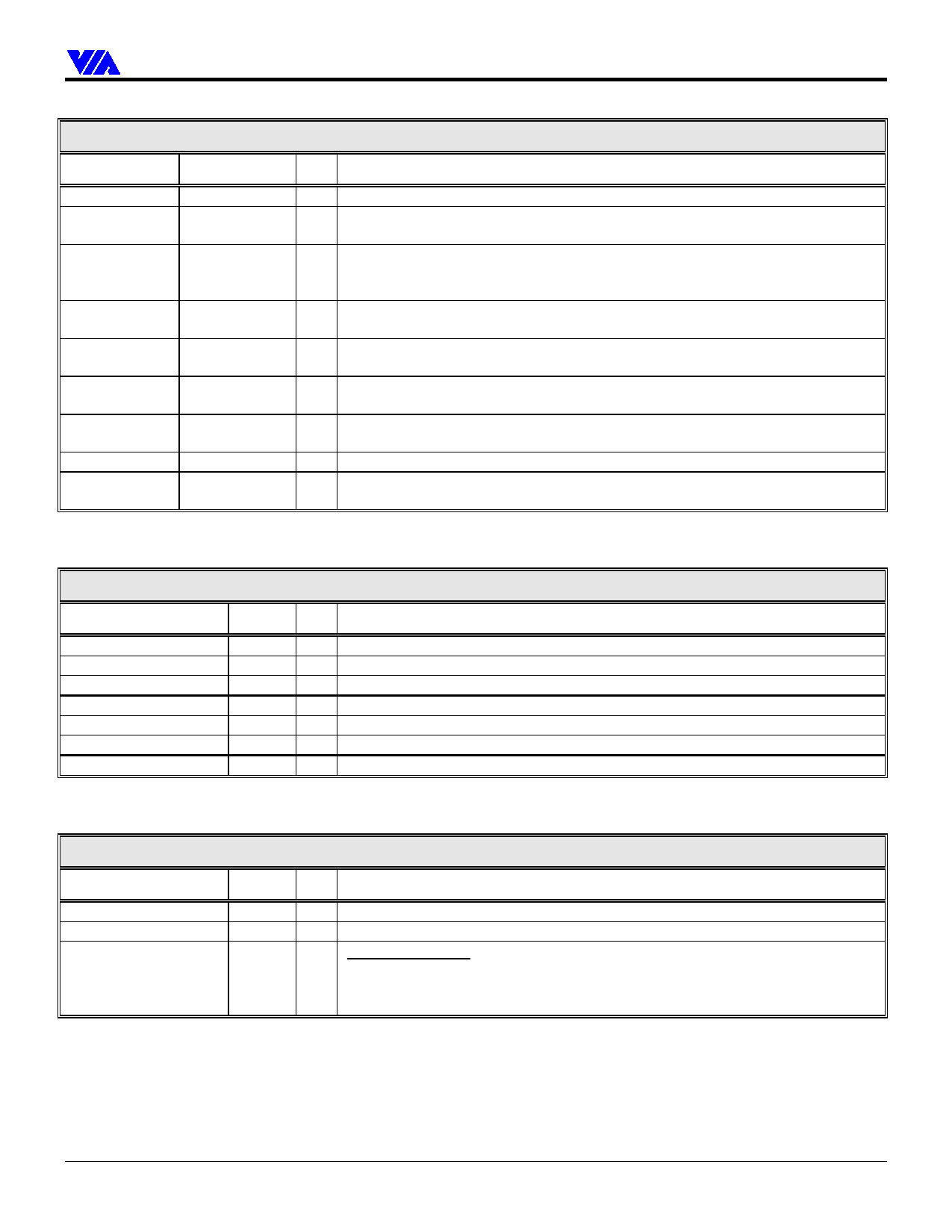

VT82C596B

Signal Name

CPURST

INTR

NMI

INIT

STPCLK#

SMI#

FERR#

IGNNE#

SLP#

Pin #

M19

L19

L20

L18

J18

P20

K19

L17

K20

CPU Interface

I/O Signal Description

OD CPU Reset. The VT82C596B asserts CPURST to reset the CPU during power-up.

OD CPU Interrupt. INTR is driven by the VT82C596B to signal the CPU that an

interrupt request is pending and needs service.

OD Non-Maskable Interrupt. NMI is used to force a non-maskable interrupt to the

CPU. The VT82C596B generates an NMI when either SERR# or IOCHK# is

asserted.

OD Initialization. The VT82C596B asserts INIT if it detects a shut-down special cycle

on the PCI bus or if a soft reset is initiated by the register

OD Stop Clock. STPCLK# is asserted by the VT82C596B to the CPU in response to

different Power-Management events.

OD System Management Interrupt. SMI# is asserted by the VT82C596B to the CPU

in response to different Power-Management events.

I Numerical Coprocessor Error. This signal is tied to the coprocessor error signal on

the CPU. Internally generates interrupt 13 if active.

OD Ignore Numeric Error. This pin is connected to the “ignore error” pin on the CPU.

OD Sleep. Used to put the CPU to sleep. Used with slot-1 CPUs only. Not currently

used with socket-7 CPUs.

Signal Name

USBP0+

USBP0-

USBOC0#

USBP1+

USBP1-

USBOC1#

USBCLK

Pin #

G2

H3

J1

F1

H2

J2

L3

Universal Serial Bus Interface

I/O Signal Description

IO USB Port 0 Data +

IO USB Port 0 Data -

I USB Port 0 Over Current Detect. Port 0 is disabled if this input is low.

IO USB Port 1 Data +

IO USB Port 1 Data -

I USB Port 1 Over Current Detect. Port 1 is disabled if this input is low.

I USB Clock. 48MHz clock input for Universal Serial Bus interface

Signal Name

SMBCLK

SMBDATA

SMBALRT# / GPI11

System Management Bus (SMB) Interface (I2C Bus)

Pin #

R19

T20

N17

I/O Signal Description

IO SMB / I2C Clock.

IO SMB / I2C Data.

I MultiFunction Pin

SMB Alert. (Rx74[5] = 0) When the chip is enabled to allow it, assertion generates

an IRQ or SMI interrupt or a power management resume event.

General Purpose Input 11. (Rx74[5] = 1) General purpose input.

Revision 0.3 June 17, 1999

-8-

Pinouts