ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

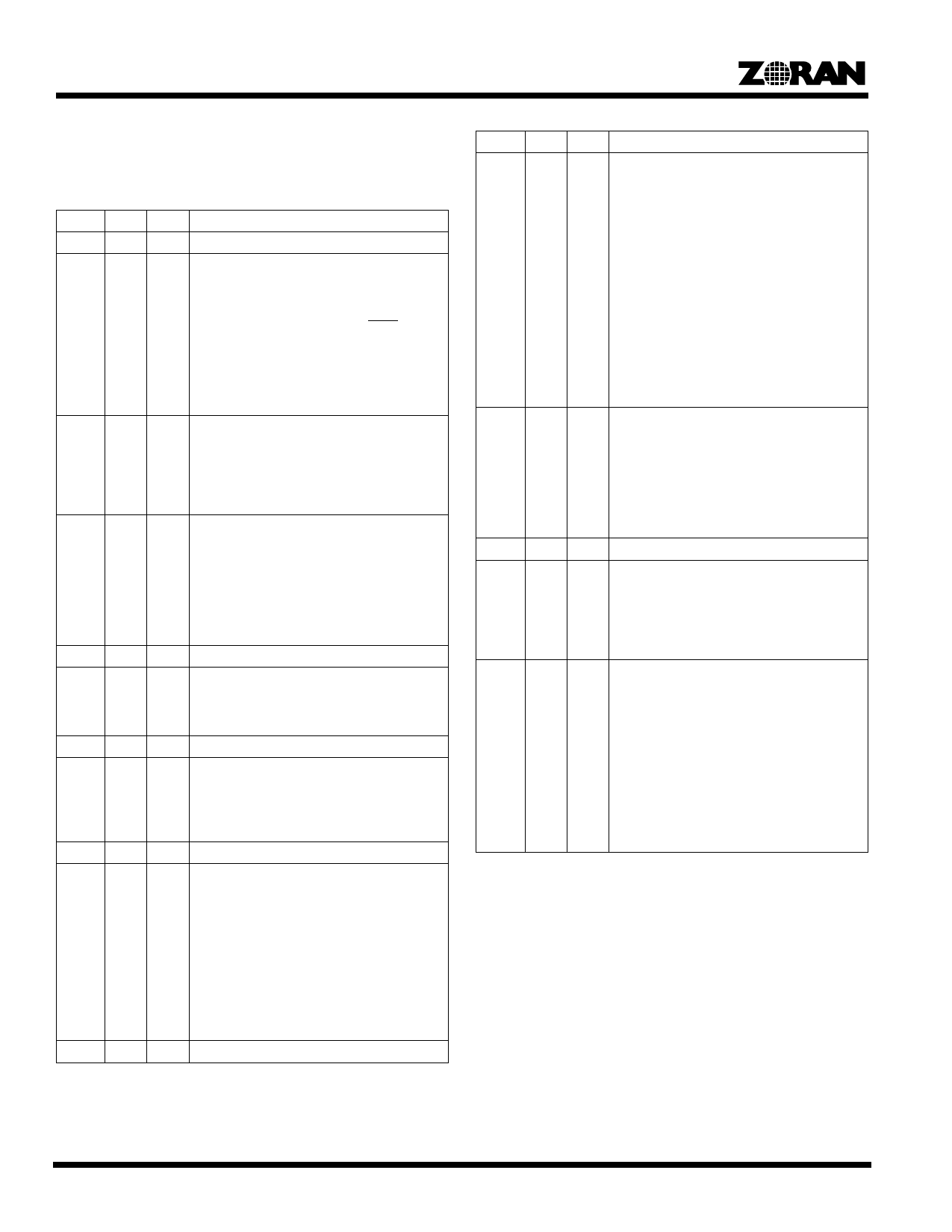

13.14 MPEG Code Transfer Control Register

This register contains status and control bits and configuration

parameters for code DMA transfers.

Address Offset: 0x034

Bit Type Mod

Description

31

R

Reserved. Returns zero.

30 RC all CodTime - MPEG Code-Write Timeout flag.

This bit is set to ‘1’ by the GuestBus master if

a code-write cycle on the GuestBus lasts

more than 64 PCI clocks. This might happen

when the accessed guest holds GWS low too

long. It is cleared (‘0’) by the host writing a ‘1’.

Priority is given to the GuestBus master in

case of concurrent accesses to this bit.

‘1’ - a code-write cycle has timed out.

‘0’ - no timeout occurred (default value).

29

R

CEmpty - Code FIFO Empty.

This bit reflects the status of the internal code

buffer. When the buffer is empty this bit

shows one, otherwise zero.

‘1’ - Buffer is empty (default value),

‘0’ - Buffer is not empty.

28 RW cod CFlush - Code FIFO Flush.

This bit is used by the host to reset the

internal code buffer. When it is asserted

remaining code in the buffer is lost.

After it is deasserted the buffer is empty and

ready to receive data.

‘1’ - flush internal code buffer (default value),

‘0’ - normal operation of buffer.

27:23 R

Reserved. Returns zero.

22:20 RW cod CodGuestID - Code Guest Identification.

These three bits select the guest to be

accessed for MPEG code DMA transfers.

Default after reset is 000b.

19

R

Reserved. Returns zero.

18:16 RW cod CodGuestReg - MPEG Code Guest Regis-

ter. Register indication of accessed guest for

MPEG code DMA transfers. Within each

guest up to eight registers can be addressed.

Default after reset is 000b.

15

R

Unused. Returns zero.

14:12 RW cod CodMemSize - MPEG Code Memory Buffer

Size. This value determines the size of the

contiguous memory buffer allocated by the

host for storage of MPEG compressed data:

000b - 8 kbyte,

001b - 16 kbyte,

010b - 32 kbyte,

011b - 64 kbyte (default value),

100b - 128 kbyte,

101b - 256 kbyte.

110b - 111b will result in the default value.

11

R

Reserved. Returns zero.

Address Offset: 0x034 (Continued)

Bit

10:8

Type

RW

Mod

cod

Description

CodMemStep - MPEG Code Memory Report

Step.

In MPEG mode, this value determines the

amount of code data, in quanta of 8 kbytes,

after which the ZR36067 notifies its position

(within the buffer) to the host, by requesting

an interrupt. For proper operation, the buffer

size must be greater than or equal to the

report step size:

000b - IRQ every 8 kbytes,

001b - IRQ every 16 kbytes (default value),

010b - IRQ every 32 kbytes,

011b - IRQ every 64 kbytes,

100b - IRQ every 128 kbytes,

101b - IRQ every 256 kbytes.

110b - 111b will result in the default value.

7

RW all CodReadEn - MPEG Code-Read Enable.

In MPEG mode, if this bit is cleared by the

host, the code-read transfers are stopped.

The current code-read pointer retains its

value.

When this bit is set to ‘1’, the ZR36067

resumes code-read transfers.

Default value is ‘0’.

6:4

R

Reserved. Returns zero.

3:1 RW cod CodTrshld - MPEG internal code FIFO

threshold. In MPEG mode, if the fullness of

the FIFO drops below this threshold value (in

doublewords) and CodReadEn is set to ‘1’, a

code-read burst is requested.

Default value is 0x6.

0

RW cod CodAutoEn - MPEG Code-Read Auto Re-

initialize Enable.

In MPEG mode, if this bit is cleared, every

time the code memory pointer reaches the

end of the allocated space (i.e. CodMemBase

plus CodMemSize) the code-read transfer is

stopped.

If the bit is set the code memory pointer is

reinitialized at the end of the allocated space

and code-read transfers run in a cyclic

manner.

Default value is ‘0’.

30