ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

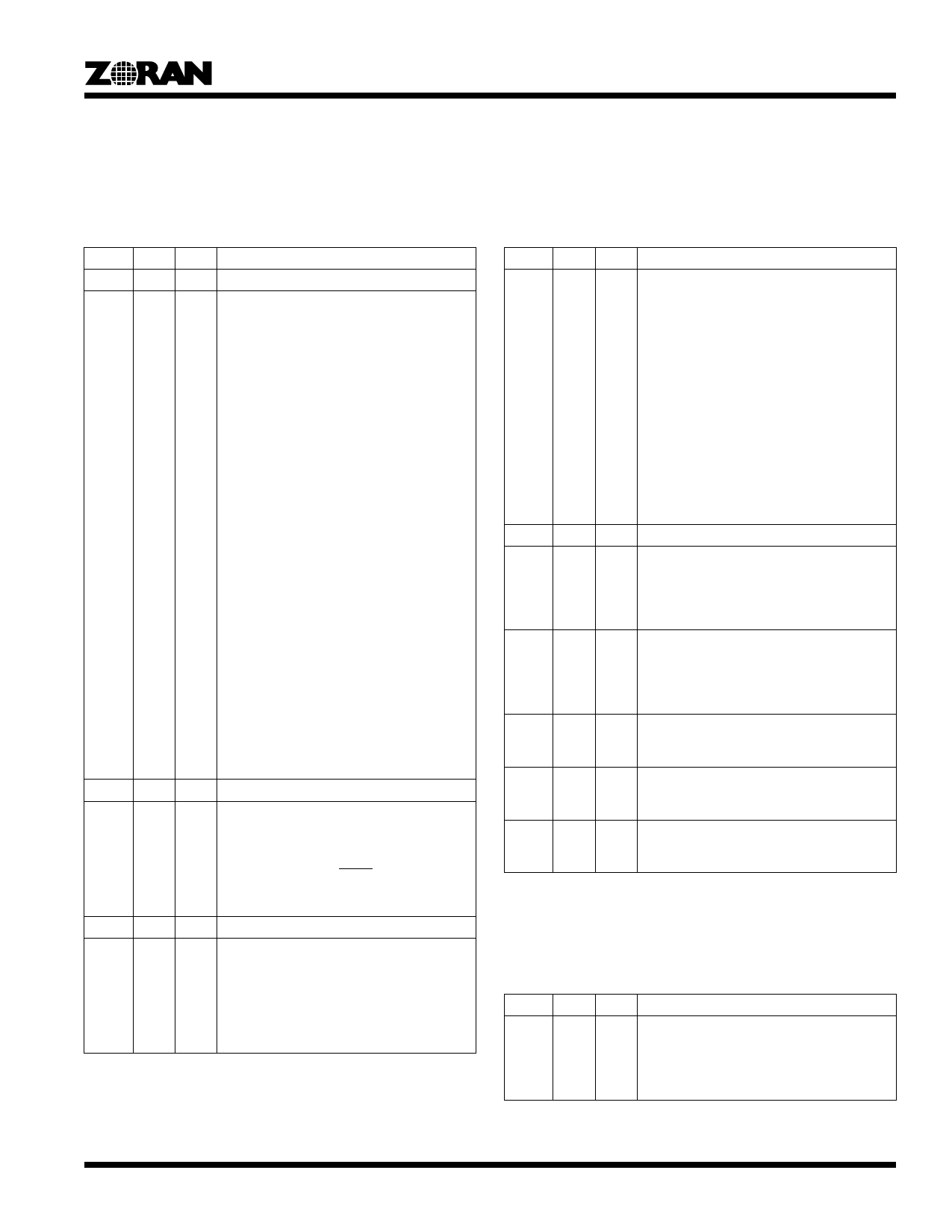

13.11 System, PCI and General Purpose Pins

Control Register

This register contains the software reset bit (byte 3), a PCI

control parameter (byte 2) and the General Purpose Pins direc-

tion parameter (byte 0).

Address Offset: 0x028

Bit Type Mod

Description

31:25 R

24 RW

23:19 R

18:16 RW

15:8 R

Reserved. Returns zero.

all SoftReset - Software Reset.

This bit is asserted by the host to reset the

ZR36067. If this bit is set to ‘0’ all resettable

registers in the device will be reset to their

default value, except:

- the SoftReset bit,

- the PCI interface.

The device continues to respond according to

the PCI Specification and can be the target of

a PCI transfer targeted at the ASRs or config.

space. The transfer (single- or burst-write)

asserting this bit will not be terminated abnor-

mally.

The device will not initiate any PCI transfers

during reset, because all DMA channels are

disabled.

This register continues to be programmable.

During reset, actually, only this bit of the

ASRs can be modified by the host (e.g.

turning reset off).

A power on (hardware) reset also asserts this

bit. After the hardware reset is over, a large

portion of the ZR36067 (see above) will

remain in reset mode until the SoftReset bit is

deasserted.

After this bit is deasserted, all registers retain

their default values, all DMA channels remain

disabled and all ASRs are programmable in

accordance with their modification condition.

‘1’ - no reset,

‘0’ - reset (default value after power on).

Reserved. Returns zero.

all WaitState - PCI Wait State Control.

This parameter defines the number of wait

states inserted by the PCI slave logic. During

each PCI transfer cycle to the ZR36067, the

device will de-assert TRDY according to this

value.

Default value 000b.

Reserved. Returns zero.

7:0 RW res GenPurDir - General Purpose Pins

Direction.

These eight bits define the direction of the

GPIO7..0 pins, respectively. A ‘1’ defines the

corresponding pin as an input, a ‘0’ as an

output.

Default value is 0xFF (all inputs).

13.12 General Purpose Pins and GuestBus Control

Register (I)

This register contains the values for General Purpose outputs

(byte 3) and timing parameters for the first four Guests (bytes

1-0).

Address Offset: 0x02C

Bit Type Mod

Description

31:24 RW

23:16 R

15:14 RW

all GenPurIO - General Purpose Input/Output.

The function of this register depends on the

setting of GenPurDir.

For each pin configured as input (default):

- reading this bit will return the current value

of the input pin.

- writing to an input has no meaning, no

change of that bit.

For each pin configured as output:

- reading this bit will return the value on the

corresponding output pin. (If there is no

external short circuit, this is the last value

written by the host.)

- writing will change the output to the value

specified.

Default value is 0xF0.

Reserved. Returns zero.

res Duration time for guest 3:

00b - Tdur3 = 3 PCI clocks (default value),

01b - Tdur3 = 4 PCI clocks,

10b - Tdur3 = 12 PCI clocks,

11b - Tdur3 = 15 PCI clocks.

13:12 RW

11:8 RW

7:4 RW

3:0 RW

res Recovery time for guest 3:

00b - Trec3 = 3 PCI clocks (default value),

01b - Trec3 = 4 PCI clocks,

10b - Trec3 = 12 PCI clocks,

11b - Trec3 = 15 PCI clocks.

res Duration and recovery times for guest 2

(same structure as defined for guest 3

above).

res Duration and recovery times for guest 1

(same structure as defined for guest 3

above).

res Duration and recovery times for guest 0

(same structure as defined for guest 3

above).

13.13 MPEG Code Source Address Register

This register contains the DWORD base address for MPEG

mode code DMA transfers.

Address Offset: 0x030

Bit Type Mod

Description

31:2 RW cod CodMemBase - MPEG Code Memory Base

1:0

R

Address. This is the source starting address

for the code-read DMA transfers.

Default value is 0xFFFFFFFC.

Bits 1..0 are hardwired to 00b.

29