ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

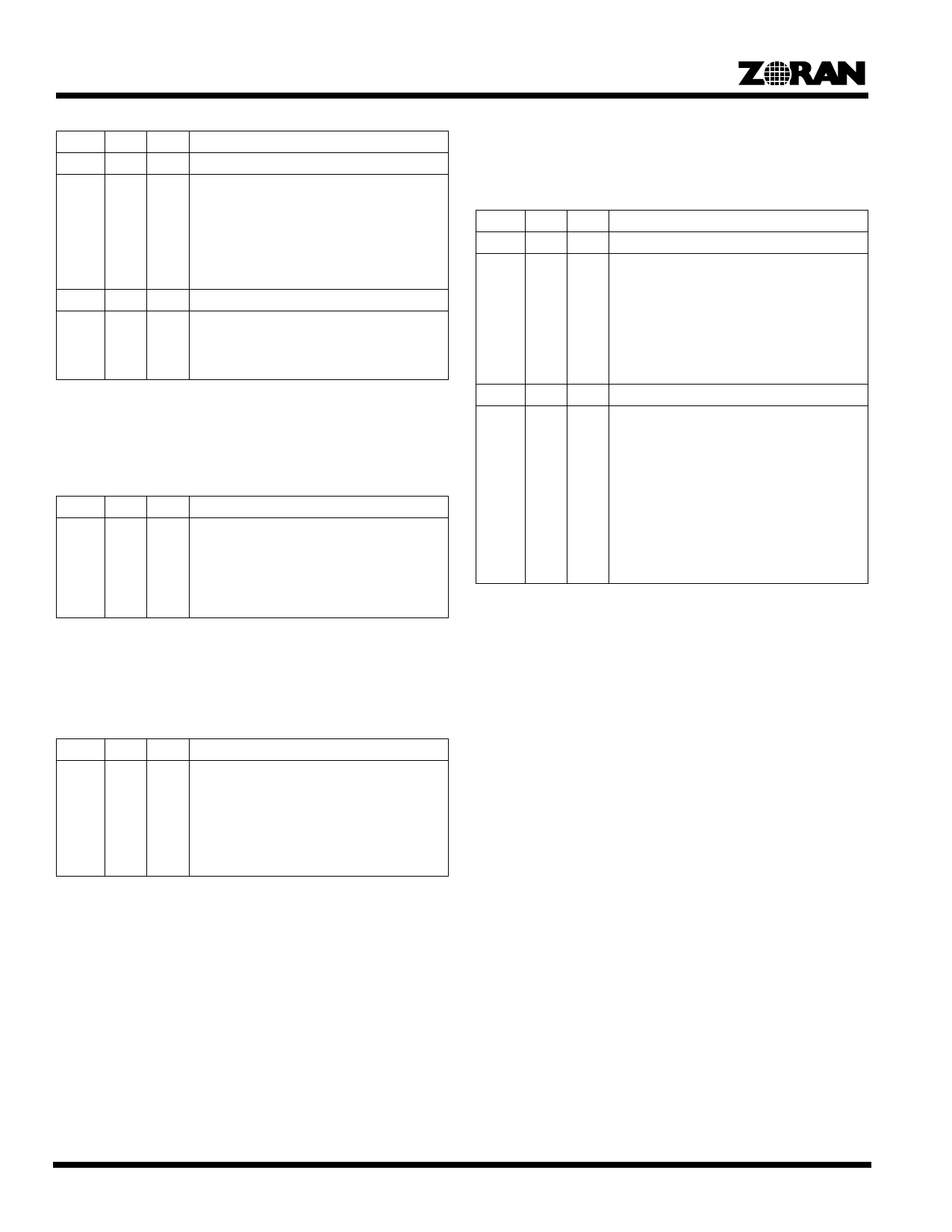

Address Offset: 0x018 (Continued)

Bit Type Mod Description

23:22 R

Reserved. Returns zero.

21:12 RW

11:10 R

vid VidWinHt - Video Window Height.

This register defines the number of lines that

should be displayed by the ZR36067.

If DispMod = 0, VidWinHt is half the number,

if DispMod = 1, it is the entire number of

display lines.

Default value is 0x0F0.

Reserved. Returns zero.

9:0 RW vid VidWinWid - Video Window Width.

This register defines the width of the video

window in number of pixels.

Default value is 0x3FF.

13.8 Masking Map “Top” Register

This register contains the DWORD base address of the top

masking map.

Address Offset: 0x01C

Bit Type Mod

Description

31:2 RW vid MaskTopBase - Masking Map Top Base

1:0

R

Address.

This is the source starting address of the top

field for the masking map read transfers.

Default value is 0xFFFFFFFC.

Bits 1..0 are hardwired to 00b.

13.10 Overlay Control Register

This register contains the parameters controlling overlay (byte 1)

and masking map addressing (byte 0).

Address Offset: 0x024

Bit

31:16

15

Type

R

RW

Mod

vid

Description

Reserved. Returns zero.

OvlEnable - Overlay Enable flag.

When enabled the masking information in the

video mask is evaluated to allow overlay of

other windows or graphics.

When disabled the video window is always on

top.

‘1’ - overlay enabled,

‘0’ - overlay disabled (default value).

14:8 R

Reserved. Returns zero.

7:0 RW vid MaskStride. This register defines the

address increment in doublewords that is

needed to get from the end of a mask line to

the beginning of the next.

If the address difference between two con-

secutive mask lines in main memory is zero

(i.e, they are physically consecutive) then

MaskStride should be set (by the driver soft-

ware) to zero (if DispMode=1) or the mask

line size in doublewords (if DispMode=0).

Default value is 0xFF.

13.9 Masking Map “Bottom” Register

This register contains the DWORD base address of the bottom

masking map.

Address Offset: 0x020

Bit Type Mod

Description

31:2 RW vid MaskBotBase - Masking Map Bottom Base

1:0

R

Address.

This is the source starting address of the

bottom field for the masking map read trans-

fers.

Default value is 0xFFFFFFFC.

Bits 1..0 are hardwired to 00b.

28