ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

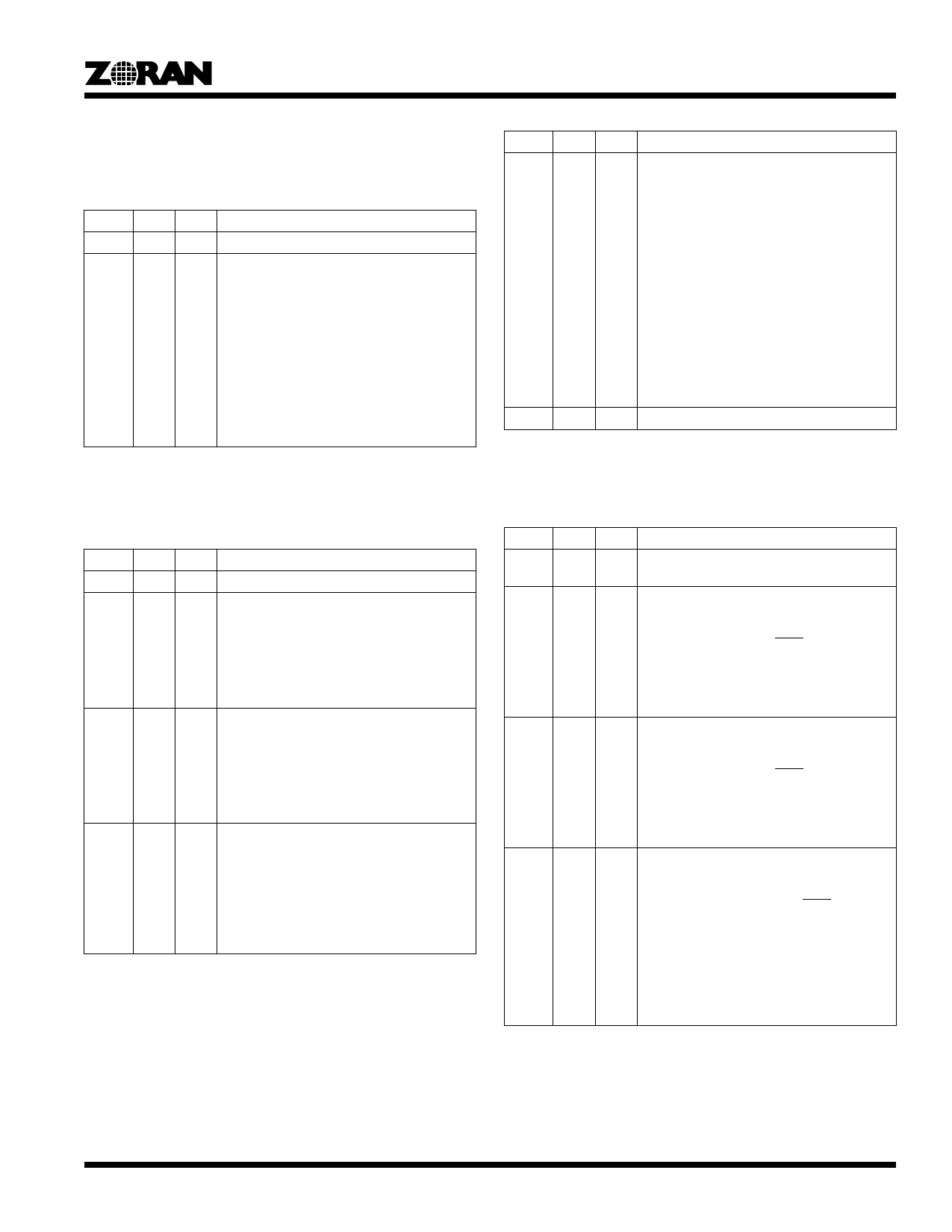

13.15 MPEG Code Memory Pointer Register

This register contains the pointer to the code memory of the host

in MPEG mode.

Address Offset: 0x038

Bit

31:16

15:0

Type

R

RW

Mod

cod

Description

Unused. Returns zero.

CodMemPoint - MPEG Code Memory

Pointer. In MPEG mode, this register reflects

the current position of the code memory

pointer within the range of the allocated host

memory. The value represents the number of

doublewords from the base address.

Writing to this register by the host can be

used for reset or moving the pointer inside the

code memory space, only if CodReadEn is

deasserted. A value pointing outside the

memory size should not be used.

Default value is zero.

13.16 Interrupt Status Register

This register contains the status of the interrupt sources.

Address Offset: 0x03C

Bit Type Mod

Description

31

R

Reserved. Returns zero.

30 RC all GIRQ1 - GIRQ1 Input Pin. A ‘1’ indicates that

a guest requested an interrupt on the GIRQ1

input pin. This bit is cleared when the host

tries to write ‘1’ to it.

In case of concurrent accesses to this bit, it

remains ‘1’.

Default value is ‘0’ (no IRQ).

29 RC all GIRQ0 - GIRQ0 Input Pin. A ‘1’ indicates that

a guest requested an interrupt on the GIRQ0

input pin. This bit is cleared when the host

tries to write ‘1’ to it.

In case of concurrent accesses to this bit, it

remains ‘1’.

Default value is ‘0’ (no IRQ).

28 RC all CodRepIRQ - MPEG Code Report Step

Interrupt Request. A ‘1’ indicates that the

code memory buffer pointer, in MPEG mode,

has passed a report step. This bit is cleared

when the host tries to write ‘1’ to it.

In case of concurrent accesses to this bit, it

remains ‘1’.

Default value is ‘0’ (no IRQ).

Address Offset: 0x03C (Continued)

Bit Type Mod

Description

27 RC all JPEGRepIRQ - JPEG Report Interrupt

Request. A ‘1’ indicates that a JPEG field/

frame process has ended.

In Compression modes, a field compression

has ended and its data has been transferred

to the allocated code buffer in system

memory.

In Decompression modes, a field/frame

decompression has ended and its corre-

sponding code buffer can be re-loaded by the

software.

This bit is cleared when the host tries to write

‘1’ to it.

In case of concurrent accesses to this bit, it

remains ‘1’.

Default value is ‘0’ (no IRQ).

26:0 R

Reserved. Returns zero.

13.17 Interrupt Control Register

This register contains the control byte for the interrupt handling.

Address Offset: 0x040

Bit Type Mod

Description

31

R

Reserved for future interrupt source. Returns

‘0’.

30 RW all GIRQ1En - GIRQ1 Enable. When enabled

and IntPinEn is set to ‘1’, each positive edge

of the GIRQ1 input will generate an interrupt

request on the PCI Bus INTA output pin.

When cleared, GIRQ1 continues to reflect the

corresponding interrupt pin.

‘1’ - GIRQ1 enabled,

‘0’ - GIRQ1 disabled (default value).

29 RW all GIRQ0En - GIRQ0 Enable. When enabled

and IntPinEn is set to ‘1’, each positive edge

of the GIRQ0 input will generate an interrupt

request on the PCI Bus INTA output pin.

When cleared, GIRQ0 continues to reflect the

corresponding interrupt pin.

‘1’ - GIRQ0 enabled,

‘0’ - GIRQ0 disabled (default value).

28 RW all CodRepIrqEn - MPEG Mode Code Report

Step Interrupt Enable. When enabled and

IntPinEn is set to ‘1’, an interrupt request will

be generated on the PCI Bus INTA output pin

each time the code memory buffer pointer

passes a report step.

When CodRepIrqEn is cleared, CodRepIrq

continues to reflect the internal report step

interrupt request.

‘1’ - interrupt request enabled,

‘0’ - disabled (default value).

31