DS2148 データシートの表示(PDF) - Maxim Integrated

部品番号

コンポーネント説明

一致するリスト

DS2148 Datasheet PDF : 73 Pages

| |||

DS2148/DS21Q48

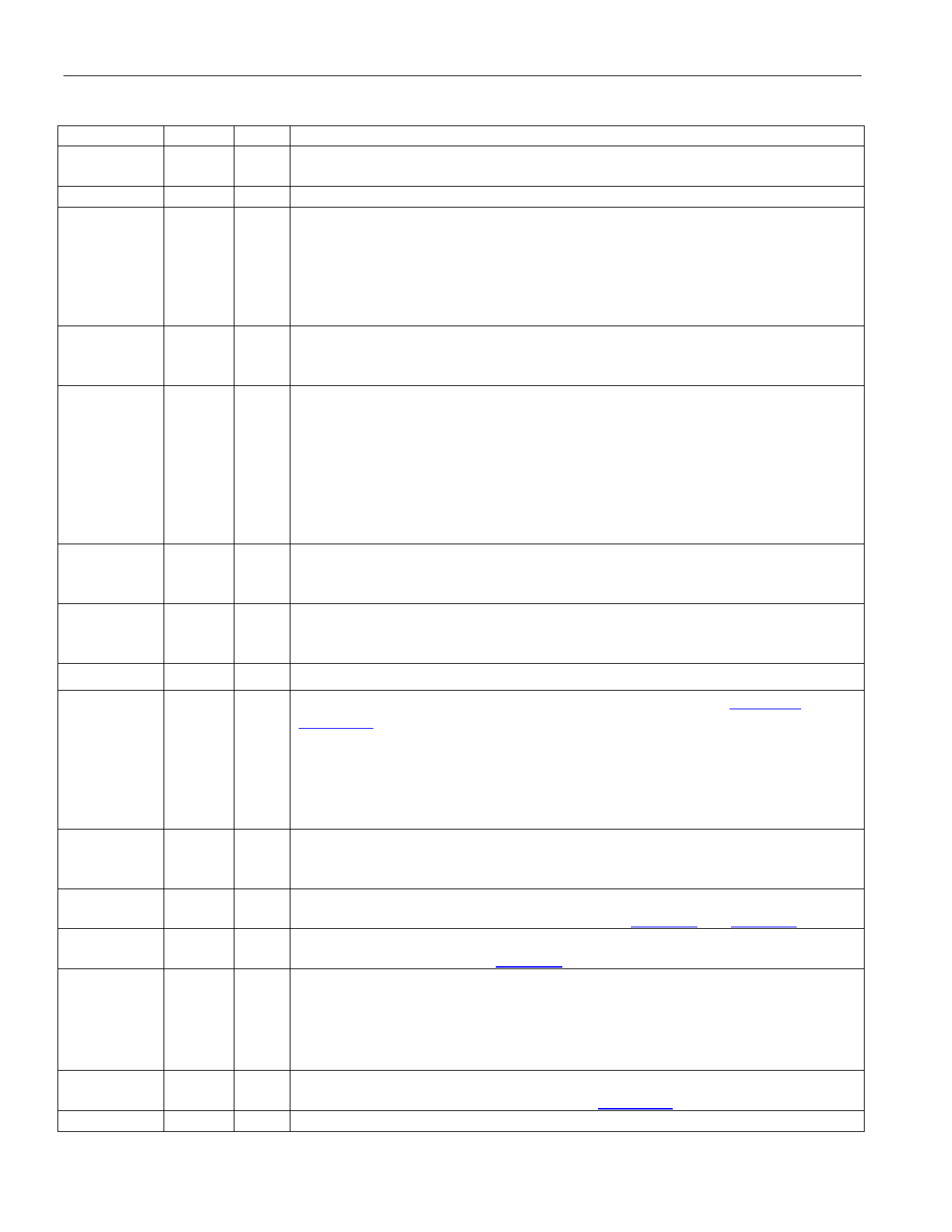

Table 2-7. Pin Description in Hardware Mode (Sorted by Pin Name, DS2148T)

NAME

BIS0/BIS1

BPCLK

CES

PIN

32/33

31

12

I/O

FUNCTION

I

Bus Interface Select Bits 0 & 1. Used to select bus interface option. BIS0 = 1

and BIS1 = 1 selects hardware mode.

O Backplane Clock. 16.384MHz output.

Receive & Transmit Clock Edge Select. Selects which RCLK edge to update

RPOS and RNEG and which TCLK edge to sample TPOS and TNEG.

I

0 = update RNEG/RPOS on rising edge of RCLK; sample TPOS/TNEG on

falling edge of TCLK

1 = update RNEG/RPOS on falling edge of RCLK; sample TPOS/TNEG on

rising edge of TCLK

Disable Jitter Attenuator

DJA

8

I 0 = jitter attenuator enabled

1 = jitter attenuator disabled

Receive Equalizer Gain Limit. This pin controls the sensitivity of the receive

equalizer.

EGL E1 (ETS = 0)

EGL

1

I

0 = -12dB (short haul)

1 = -43dB (long haul)

EGL T1 (ETS = 1)

0 = -36dB (long haul)

1 = -30dB (limited long haul)

E1/T1 Select.

ETS

2

I 0 = E1

1 = T1

HBE

Receive & Transmit HDB3/B8ZS Enable.

11

I 0 = enable HDB3 (E1)/B8ZS (T1)

1 = disable HDB3 (E1)/B8ZS (T1)

HRST

29

I Hardware Reset. Bringing HRST low will reset the DS2148.

Jitter Attenuator MUX. Controls the source for JACLK. See Figure 1-1 and

Table 2-13.

E1 (ETS = 0)

JAMUX

JAMUX

9

I MCLK = 2.048MHz 0

T1 (ETS = 1)

MCLK = 2.048MHz 1

MCLK = 1.544MHz 0

Jitter Attenuator Select

JAS

10

I 0 = place the jitter attenuator on the receive side

1 = place the jitter attenuator on the transmit side

L0/L1/L2 7/6/5

I

Transmit LIU Waveshape Select Bits 0 & 1 [H/W Mode]. These inputs

determine the waveshape of the transmitter. See Table 7-1 and Table 7-2.

LOOP0/

LOOP1

16/17

I

Loopback Select Bits 0 & 1 [H/W Mode]. These inputs determine the active

loopback mode (if any). See Table 2-8.

MCLK

Master Clock. A 2.048MHz (±50ppm) clock source with TTL levels is applied

at this pin. This clock is used internally for both clock/data recovery and for jitter

30

I attenuation. Use of a T1 1.544MHz clock source is optional. G.703 requires an

accuracy of ±50ppm for both T1 and E1. TR62411 and ANSI specs require an

accuracy of ±32ppm for T1 interfaces.

MM0/MM1 18/19

I

Monitor Mode Select Bits 0 & 1 [H/W Mode]. These inputs determine if the

receive equalizer is in a monitor mode. See Table 2-11.

NA

-

I Not Assigned. Should be tied low.

18 of 73