UPD72862 データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

一致するリスト

UPD72862 Datasheet PDF : 36 Pages

| |||

µPD72862

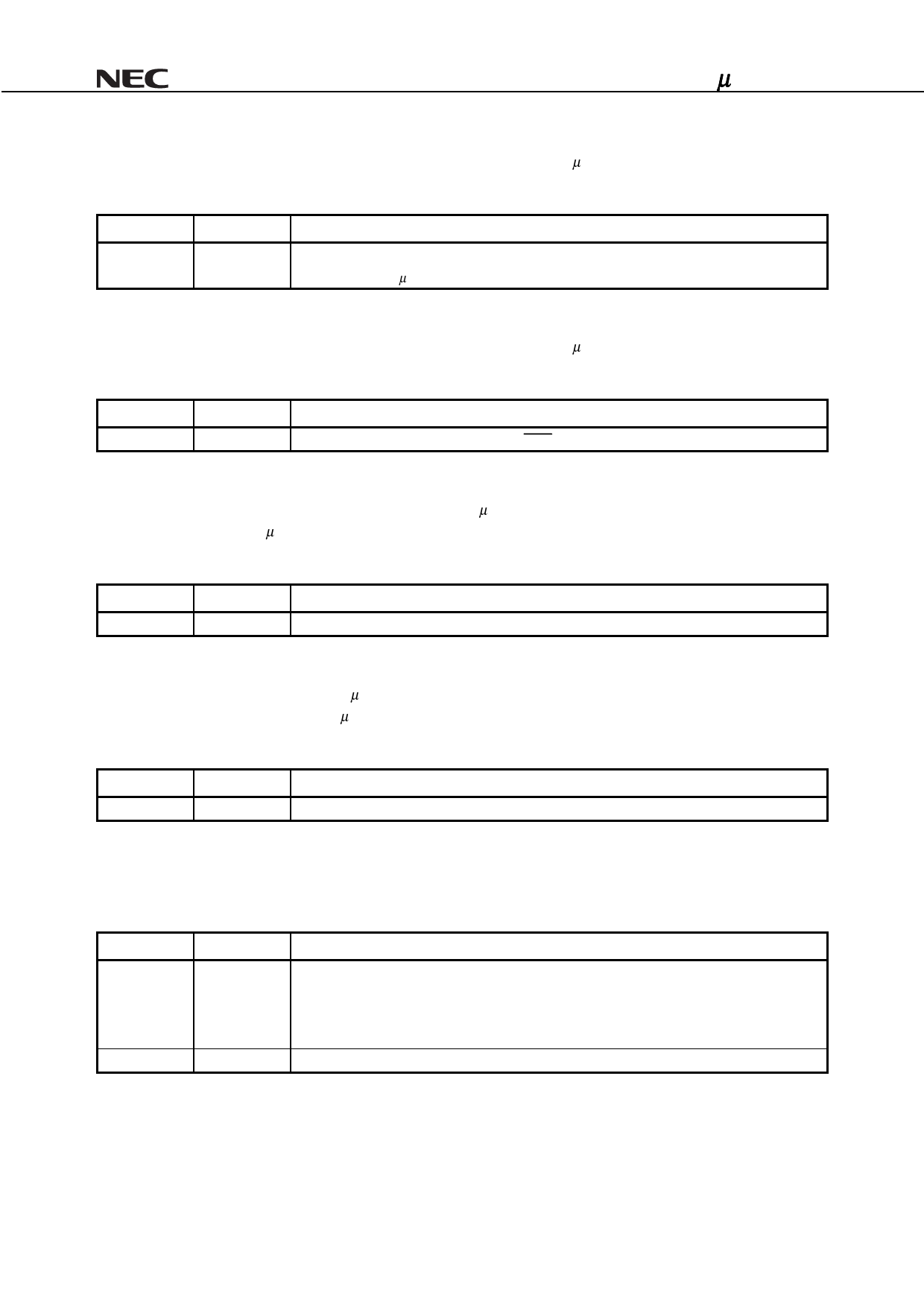

2.1.16 Offset_3C Interrupt Line Register

This register provides the interrupt line routing information specific to the µPD72862, the NEC’s implementation of

the 1394 OpenHCI specification.

Bits

7-0

R/W

Description

R/W

Default value of 00H. It specifies which input of the host system interrupt controller the

interrupt pin of the µPD72862 is connected to.

2.1.17 Offset_3D Interrupt Pin Register

This register provides the interrupt line routing information specific to the µPD72862, the NEC’s implementation of

the 1394 OpenHCI specification.

Bits

7-0

R/W

Description

R

Constant value of 01H. It specifies PCI INTA is used for interrupting the host system.

2.1.18 Offset_3E Min_Grant Register

This register specifies how long of a burst period the µPD72862 needs, assuming a clock rate of 33MHz.

Resolution is in units of ¼ µs. The value should be loaded into the register from the external serial EEPROM upon

power-up reset, and access to this register through PCI-bus is prohibited.

Bits

7-0

R/W

Description

R

Default value of 00H. Its value contributes to the desired setting for Latency Timer value.

2.1.19 Offset_3F Max Lat Register

This register specifies how often the µPD72862 needs to gain access to the PCI-bus, assuming a clock rate of

33MHz. Resolution is in units of ¼ µs. The value should be loaded into the register from the external serial

EEPROM after hardware reset, and access to this register through PCI-bus is prohibited.

Bits

7-0

R/W

Description

R

Default value of 00H. Its value contributes to the desired setting for Latency Timer value.

2.1.20 Offset_40 PCI_OHCI_Control Register

This register specifies the control bits that are IEEE1394 OpenHCI specific. Vendor options are not allowed in this

register. It is reserved for OpenHCI use only.

Bits

0

31-1

R/W

Description

R/W

PCI global SWAP Default value of 0. When this bit is 1, all quadrates read from and written to

the PCI Interface are byte swapped, thus a “PCI Global Swap”. PCI addresses for expansion

ROM and PCI Configuration registers, are, however, unaffected by this bit. This bit is not

required for motherboard implementations.

R

Reserved Constant value of all 0.

16

Data Sheet S14265EJ2V0DS00