UPD72862 データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

一致するリスト

UPD72862 Datasheet PDF : 36 Pages

| |||

µPD72862

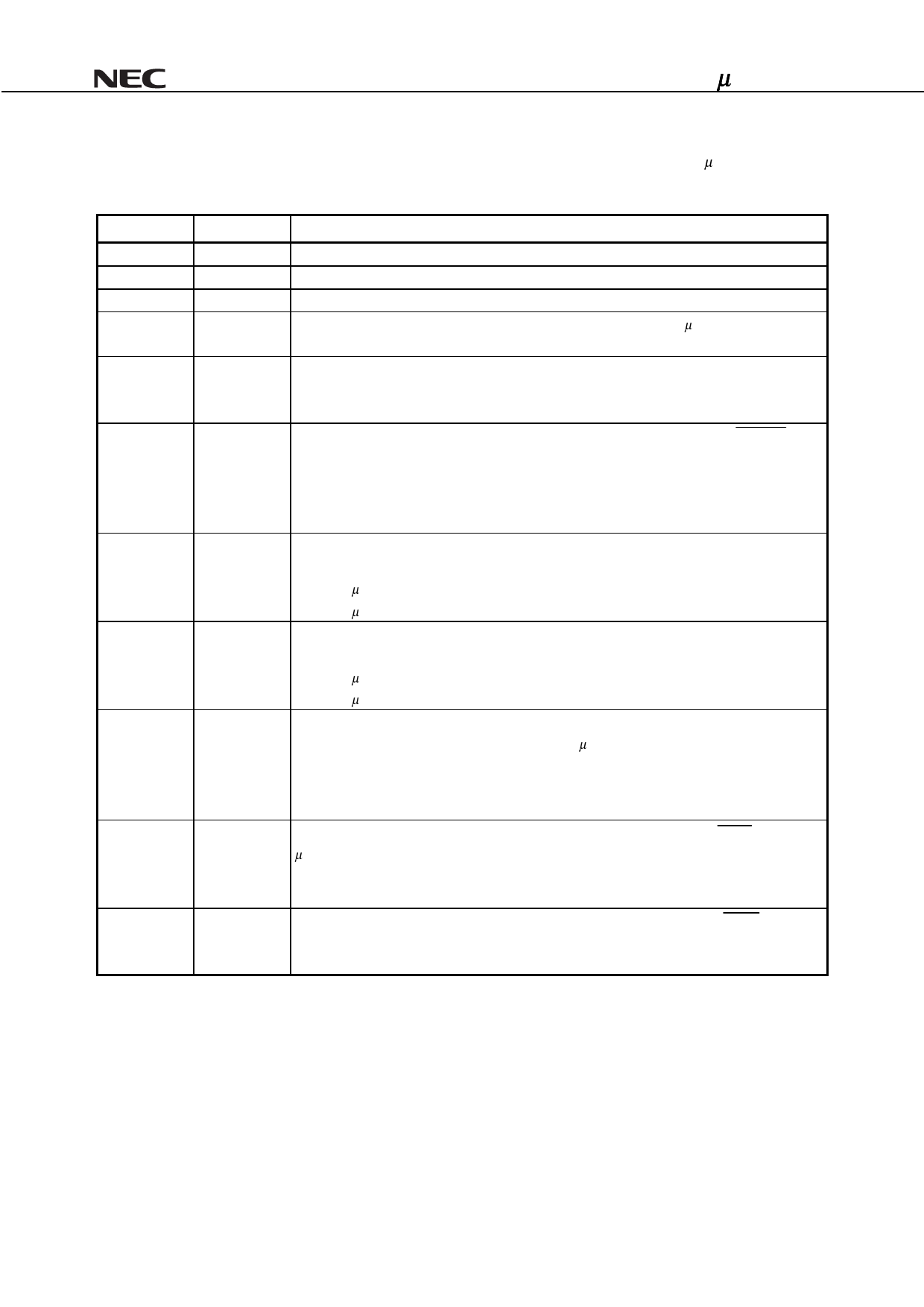

2.1.4 Offset_06 Status Register

This register tracks the status information of PCI-bus related events which are relevant to the µPD72862. “Read”

and “Write” are handled somewhat differently.

Bits

3-0

4

6,5

7

8

10,9

11

12

13

14

15

R/W

Description

R

Reserved Constant value of 0000.

R

New capabilities Constant value of 1. It indicates the existence of the Capabilities List.

R

Reserved Constant value of 00.

R

Fast back-to-back capable Constant value of 1. It indicates that the µPD72862, as a target,

cannot accept fast back-to-back transactions when the transactions are not to the same agent.

R/W

Signaled parity error Default value of 0. It indicates the occurrence of any “Data Parity”.

0: No parity detected (default)

1: Parity detected

R

DEVSEL timing Constant value of 01. These bits define the decode timing for DEVSEL.

0: Fast (1 cycles)

1: Medium (2 cycles)

2: Slow (3 cycles)

3: undefined

R/W

Signaled target abort Default value of 0. This bit is set by a target device whenever it

terminates a transaction with “Target Abort”.

0: The µPD72862 did not terminate a transaction with Target Abort

1: The µPD72862 has terminated a transaction with Target Abort

R/W

Received target abort Default value of 0. This bit is set by a master device whenever its

transaction is terminated with a “Target Abort”.

0: The µPD72862 has not received a Target Abort

1: The µPD72862 has received a Target Abort from a bus-master

R/W

Received master abort Default value of 0. This bit is set by a master device whenever its

transaction is terminated with “Master Abort”. The µPD72862 asserts “Master Abort” when a

transaction response exceeds the time allocated in the latency timer field.

0: Transaction was not terminated with a Master Abort

1: Transaction has been terminated with a Master Abort

R/W

Signaled system error Default value of 0. It indicates that the assertion of SERR by the

µPD72862.

0: System error was not signaled

1: System error was signaled

R/W

Received parity error Default value of 0. It indicates the occurrence of any PERR.

0: No parity error was detected

1: Parity error was detected

Data Sheet S14265EJ2V0DS00

13