EM78P569 データシートの表示(PDF) - ELAN Microelectronics

部品番号

コンポーネント説明

一致するリスト

EM78P569 Datasheet PDF : 58 Pages

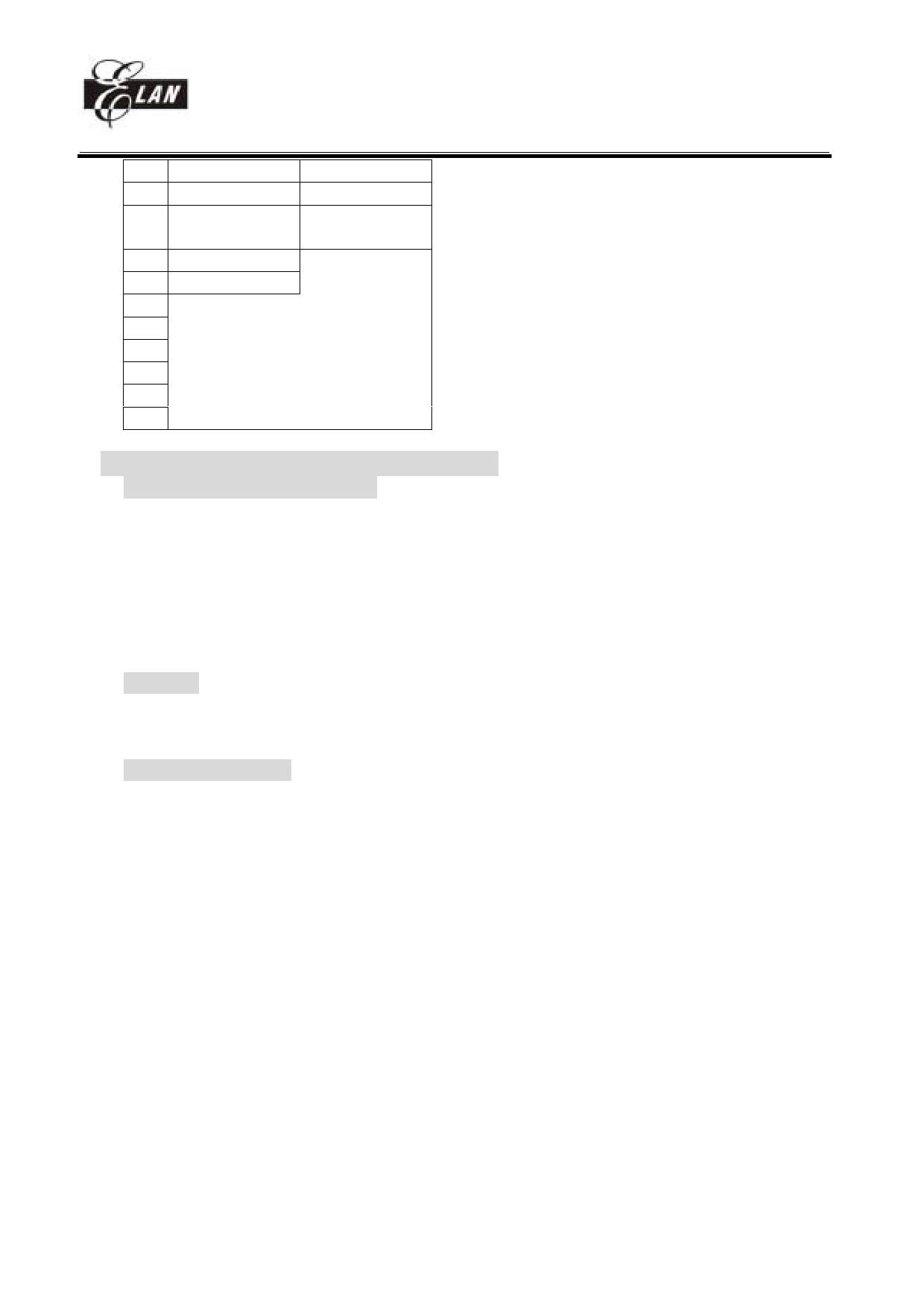

| |||

EM78P569

8-bit OTP Micro-controller

0B PortB I/O control

0C PortC I/O control

0D

0E Interrupt mask

0F Interrupt mask

10

:

1F

20

:

3F

ADC control

Port5,8,B,C switch

Clock source(CN1,CN2)

Prescaler(CN1,CN2)

VII.2 Operational Register Detail Description

R0 (Indirect Addressing Register)

R0 is not a physically implemented register. It is used as indirect addressing pointer. Any instruction using R0

as register actually accesses data pointed by the RAM Select Register (R4).

Example:

Mov A, @0x20

;store a address at R4 for indirect addressing

Mov 0x04, A

Mov A, @0xAA ;write data 0xAA to R20 at bank0 through R0

Mov 0x00, A

R1 (TCC)

TCC data buffer. Increased by 16.384KHz or by the instruction cycle clock (controlled by CONT register).

Written and read by the program as any other register.

R2 (Program Counter)

The structure is depicted in Fig.3.

Generates 16k × 13 on-chip PROGRAM OTP-ROM addresses to the relative programming instruction codes.

"JMP" instruction allows the direct loading of the low 10 program counter bits.

"CALL" instruction loads the low 10 bits of the PC, PC+1, and then push into the stack.

"RET'' ("RETL k", "RETI") instruction loads the program counter with the contents at the top of stack.

"MOV R2, A" allows the loading of an address from the A register to the PC, and the ninth and tenth bits are

cleared to "0''.

"ADD R2,A" allows a relative address be added to the current PC, and contents of the ninth and tenth bits are

cleared to "0''.

"TBL" allows a relative address added to the current PC, and contents of the ninth and tenth bits don't change.

The most significant bit (A10~A13) will be loaded with the contents of bit PS0~PS3 in the status register (R5

PAGE0) upon the execution of a "JMP'', "CALL'', "ADD R2, A'', or "MOV R2, A'' instruction.

If an interrupt is triggered, PROGRAM ROM will jump to address 0x08 at page0. The CPU will store ACC,

R3 status and R5 PAGE automatically, and they will be restored after instruction RETI.

__________________________________________________________________________________________________________________________________________________________________

* This specification is subject to be changed without notice.

8

8/19/2004 V4.4