ISP1562 データシートの表示(PDF) - NXP Semiconductors.

部品番号

コンポーネント説明

一致するリスト

ISP1562 Datasheet PDF : 94 Pages

| |||

NXP Semiconductors

ISP1562

HS USB PCI host controller

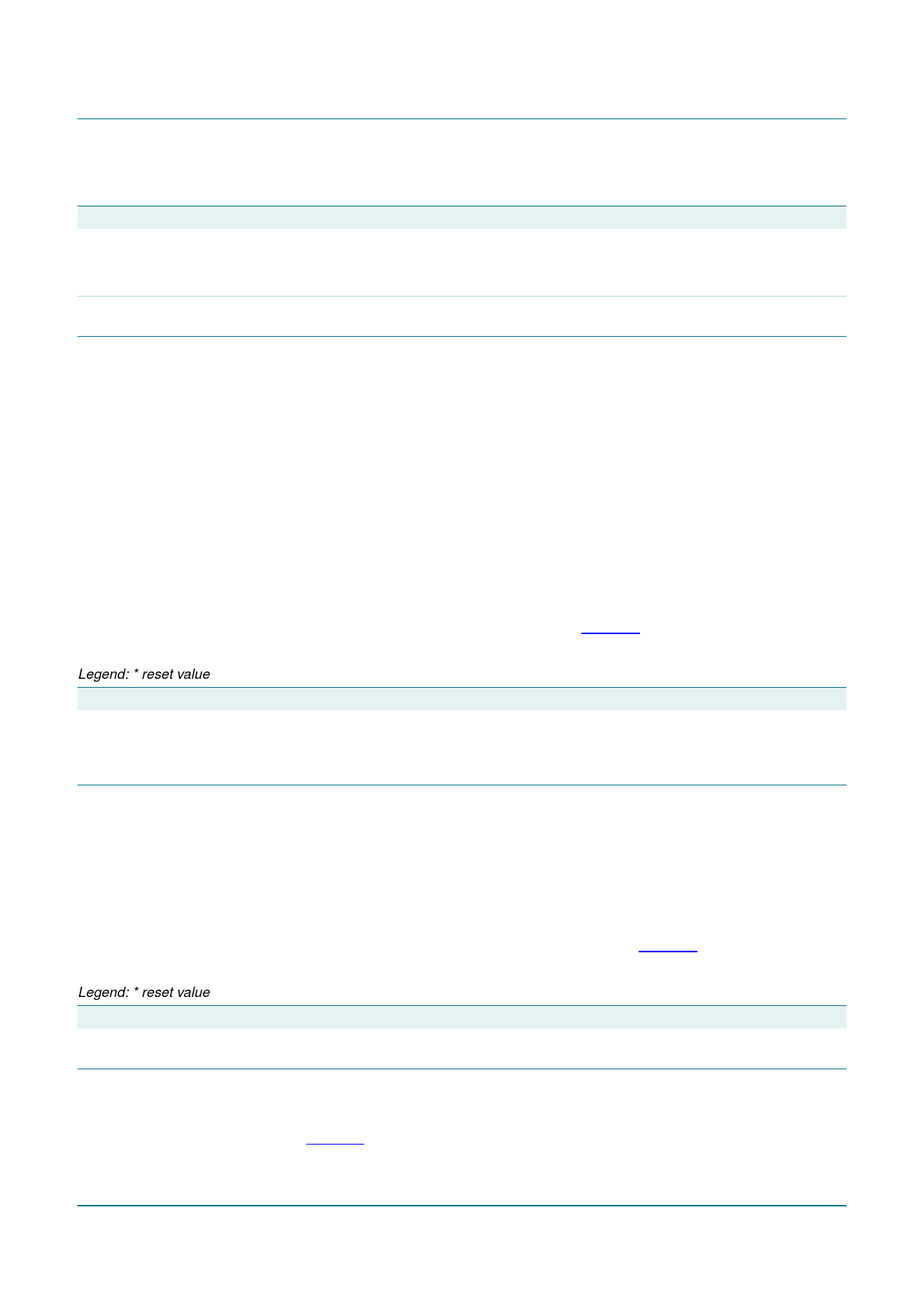

Table 16. HT - Header Type register (address 0Eh) bit description

Bit

Symbol Description

7

MFD

Multi-Function Device: This bit identifies a multifunction device.

0 — The device has single function.

1 — The device has multiple functions.

6 to 0 HT[6:0]

Header Type: These bits identify the layout of the part of the predefined header, beginning at byte 10h

in configuration space.

8.2.1.10 Base Address register 0

Power-up software must build a consistent address map before booting the machine to an

operating system. This means it must determine how much memory is in the system, and

how much address space the I/O controllers in the system require. After determining this

information, power-up software can map the I/O controllers into reasonable locations and

proceed with system boot. To do this mapping in a device-independent manner, base

registers for this mapping are placed in the predefined header portion of configuration

space.

Bit 0 in all Base Address registers is read-only and used to determine whether the register

maps into memory or I/O space. Base Address registers that map to memory space must

return logic 0 in bit 0. Base Address registers that map to I/O space must return logic 1 in

bit 0.

The bit description of the BAR0 register is given in Table 17.

Table 17. BAR0 - Base Address register 0 (address 10h) bit description

Legend: * reset value

Bit

Symbol

Access Value

Description

31 to 0 BAR0[31:0] R/W

0000 0000h*

Base Address to Memory-Mapped Host Controller Register Space:

The memory size required by OHCI and EHCI are 4 kB and 256 bytes,

respectively. Therefore, BAR0[31:12] is assigned to the two OHCI ports,

and BAR0[31:8] is assigned to the EHCI port.

8.2.1.11 Subsystem Vendor ID register

The Subsystem Vendor ID register is used to uniquely identify the expansion board or

subsystem where the PCI device resides. This register allows expansion board vendors to

distinguish their boards, even though the boards may have the same vendor ID and device

ID.

Subsystem vendor IDs are assigned by PCI-SIG to maintain uniqueness. The bit

description of the Subsystem Vendor ID register is given in Table 18.

Table 18. SVID - Subsystem Vendor ID register (address 2Ch) bit description

Legend: * reset value

Bit

Symbol Access Value Description

15 to 0 SVID[15:0] R

1131h*

Subsystem Vendor ID: 1131h is the subsystem Vendor ID assigned to

NXP Semiconductors.

8.2.1.12 Subsystem ID register

Subsystem ID values are vendor specific. The bit description of the Subsystem ID register

is given in Table 19.

ISP1562_3

Product data sheet

Rev. 03 — 14 November 2008

© NXP B.V. 2008. All rights reserved.

20 of 93