ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

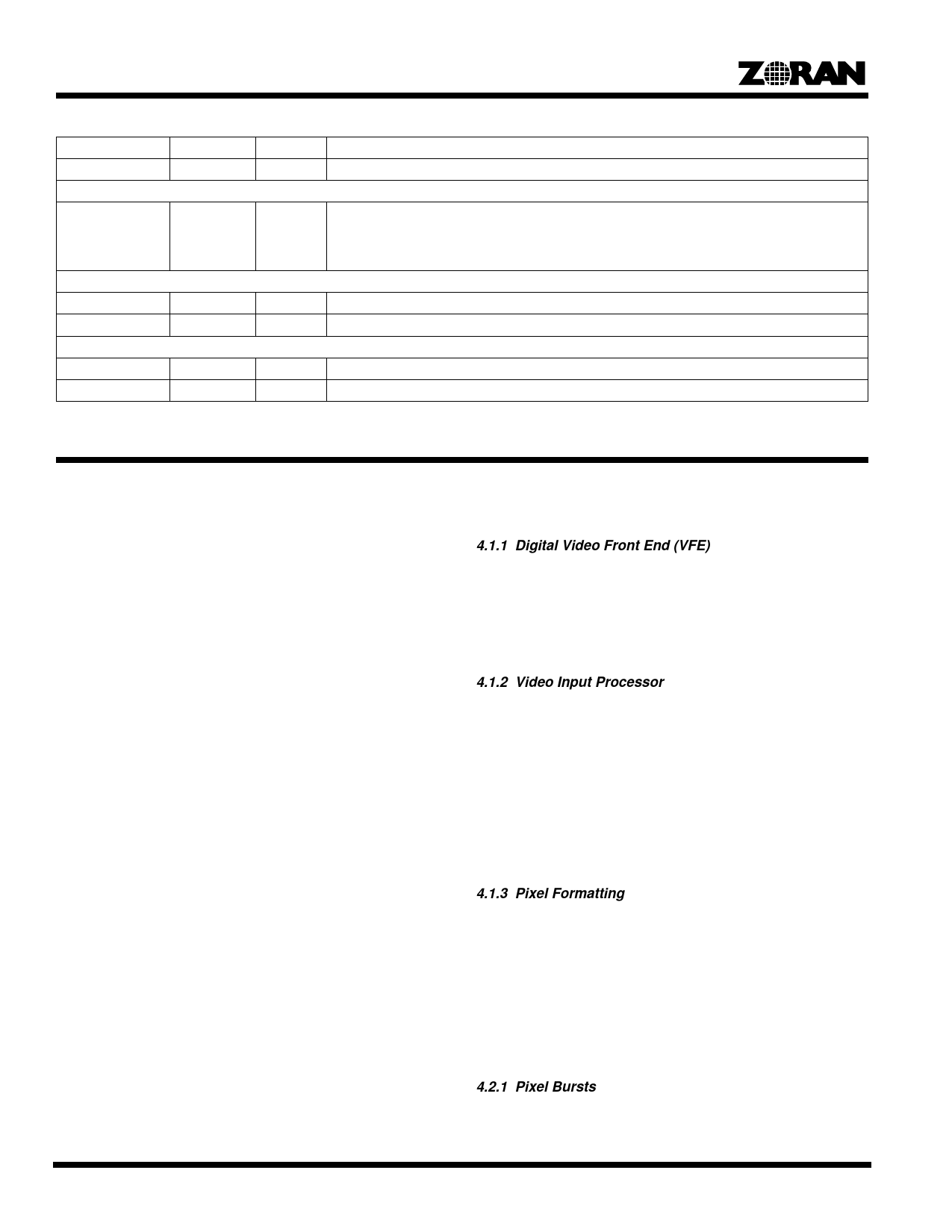

3.0 PIN DESCRIPTIONS (CONTINUED)

Symbol

SCL

Type [1]

OD

Direction

Description

I/O

I2C bus clock (qualifies for a single master operation only).

General Purpose Programmable Inputs/Outputs (8 pins)

GPIO[7:0]

3-state

I/O

General purpose input/output pins. After hardware or software reset all 8 pins are configured as

inputs. Their logical levels are reflected as register bits. Any of the pins can be configured as

output. In this state its logical level is driven by a register bit. These pins may be used to monitor

or control various board-level functions. Also used to program the high byte of Subsystem ID.

Test Pins (2 pin)

ENID

Test

I

Used for IDD test. In normal operation must be connected to GND.

TEST

Test

I

Test pin used in test mode only. In normal operation must be connected to GND.

Power (80 pins)

GND

ground

Ground (50 pins).

VDD

power

Power supply (5V) (30 pins).

1. I - standard input-only • O - standard active driver • 3-state - bidirectional I/O pin • 3-state* - a special type of 3-state, as defined in the PCI spec. May be driven by

only one PCI agent at any time • OD - open drain, may be shared by multiple drivers, as a wired-or.

4.0 FUNCTIONAL OVERVIEW

The ZR36067 multimedia controller performs the following

functions:

• Interfacing to a YUV 4:2:2 digital video bus (e.g., Phillips

SAA7110 or SAA7111).

• Video DMA channel for burst transfers of video pixels.

• Independent horizontal and vertical downscaling of the input

image, with optional horizontal filtering.

• Optional sync mastering with configurable HSYNC and

VSYNC pulse widths and polarity.

• Conversion of the YUV 4:2:2 digital video input into one of

the following pixel formats: YUV 4:2:2, RGB 5,6,5, RGB

5,5,5 or RGB 8,8,8 (packed or unpacked).

• Overlay support: any number of video pixels can be masked

off, letting the corresponding graphics pixels appear instead

of them.

• Frame grabbing.

• Two display modes: emulation of the interlaced input video,

or a single field display.

• Bidirectional Code DMA transfer with support for fragmented

code buffers.

• Control of the ZR36060 Motion JPEG Codec or ZR36050/

ZR36016 Motion JPEG chip set.

The ZR36067 supports digital video in CCIR 601 or square pixel

formats, following either the NTSC or PAL video standard. Other

non-standard input schemes are supported as well.

The functional description below follows the block diagram.

4.1 Digital Video Path

4.1.1 Digital Video Front End (VFE)

The VFE samples the incoming YUV 4:2:2 video data and sync

signals with a flexible sampling scheme, that makes it compati-

ble with a wide variety of digital video sources. The digital input

video can be cropped. The input resolutions supported by the

VFE range from 32x32 to 1023x1023, in increments of one pixel.

4.1.2 Video Input Processor

The chroma components of the video data are upsampled to

YUV 4:4:4 format. All components are horizontally filtered. Five

filtering schemes are implemented, with different parameters for

chrominance and luminance samples. Horizontal and vertical

downscaling is available if required. The vertical downscaling

can be optimized for live video or full screen Motion JPEG play-

back, in which each field is independent, or for the output of an

MPEG-1 decoder, which duplicates fields to produce its inter-

laced video output.

4.1.3 Pixel Formatting

The filtered and scaled video is converted to the desired color

space and packed according to the selected pixel format. YUV

4:2:2, 24-bit RGB (packed or unpacked) and 15- and 16-bit RGB

are supported. An error diffusion algorithm can be applied to the

RGB 5,5,5 and 5,6,5, in order to eliminate quantization artifacts

on the output image.

4.2 Video DMA Controller

4.2.1 Pixel Bursts

The packed pixels are transferred directly to the display memory

(or to the system memory), using PCI DMA bursts. Both Little

8