ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

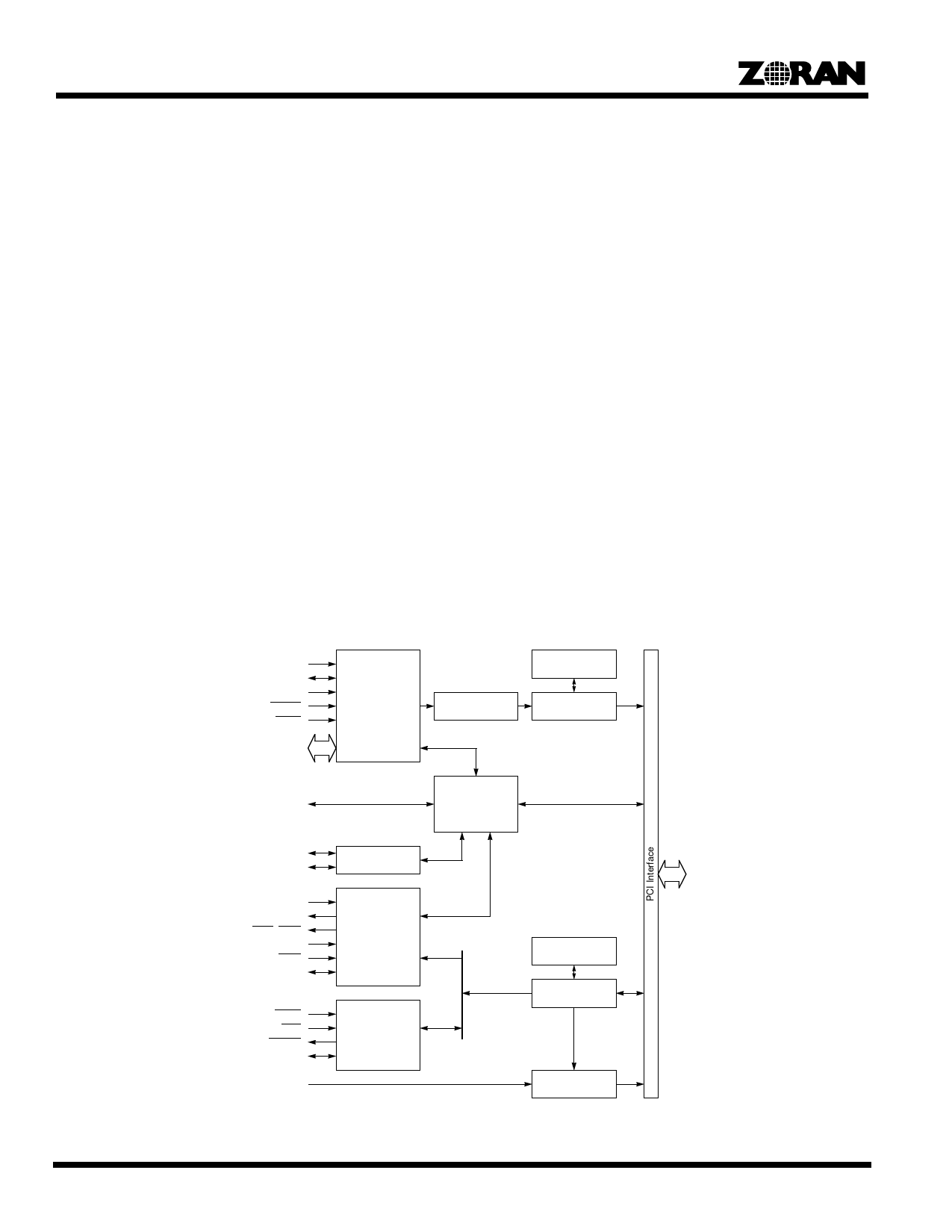

2.0 ARCHITECTURAL OVERVIEW

The ZR36067 architecture contains two main data paths, the

video path and the code path. The incoming video is processed

along the video path and transferred to the graphics display

memory using PCI DMA bursts.

The ZR36067 Video Front End samples the video bus within a

programmable active field window, defined with respect to the

video synchronization signals. An optional vertical and horizon-

tal smooth scale down can be applied, in order to support

variable image sizes and variable PCI video data rate. The

scaled video stream can be converted to various RGB formats.

The converted pixels are packed and stored in a 256-byte Video

FIFO, organized as 64 32-bit doublewords. The stored video

pixels are read from the Video FIFO and transferred to the

graphics display memory according to a display masking map

controlled by and stored inside the ZR36067.

The Code path is bidirectional. The data flow direction depends

on the mode of operation. The code stream (MPEG or JPEG) is

transferred between system memory and the internal Code

FIFO of the ZR36067 using PCI DMA bursts. The ZR36067

controls the transfer and addressing in both directions. The

Code FIFO size is 640 bytes, organized as 160 doublewords.

In JPEG Compression modes the ZR36067 Codec Front End

fills the Code FIFO. From the Code FIFO the code is transferred

to the system memory, field by field.

In JPEG Decompression modes the code stream flows in the

opposite direction, from the system memory to the ZR36067

Code FIFO. The Codec Front End reads out the Code FIFO byte

by byte onto the Code Bus.

In MPEG Playback mode, the code stream is transferred to the

ZR36067 Code FIFO from the system memory. The code bytes

are read from the Code FIFO out to the Guest Bus.

The ZR36067 video and the code paths operate simultaneously

while the ZR36067 arbitrates the PCI bus requests for each

process.

Besides managing the Video and Code paths, the ZR36067

bridges the host CPU to peripheral devices (known as Guests).

Using a dedicated handshaking mechanism (the “PostOffice”

mechanism), host accesses to an internal ZR36067 register are

reflected to the Guest Bus in order to enable indirect host read

and write operations to the Guests.

The ZR36067 contains a dedicated “Still Transfer” port which

enables data flow between the PCI interface and the Video Front

End. Using a specific handshake protocol, the host software

may transfer digitized video (RGB pixels) from the system

memory to the Video bus, and vice versa. This path enables very

fast transfer of still video images to be compressed or decom-

pressed by the JPEG codec.

VCLK, VCLKx2

VSYNC, HSYNC

FI

RTBSY

START, PXEN

Y[7:0]

UV[7:0]

B[7:0]

GPIO[7:0]

SCL

SDA

GCS[7:0]

GAD[2:0]

GRD, GWR

GRDY

GWS

GDAT[7:0]

CEND

CCS

CBUSY

CODE[7:0]

GIRQ[1:0]

Video Front End

(VFE)

Video Input

Processor

Video DMA

Controller

Video FIFO

I2C Port

Application

Specific

Registers

Guest Bus

Master

Code DMA

Controller

Code FIFO

Codec Front End

(CFE)

Interrupt

Manager

Figure 2. ZR36067 Block Diagram

6