ZR36067 データシートの表示(PDF) - Unspecified

部品番号

コンポーネント説明

一致するリスト

ZR36067 Datasheet PDF : 48 Pages

| |||

AV PCI CONTROLLER

Codec bus to the system memory; in JPEG Decompression,

from the system memory to the Codec bus.

The JPEG code data inside the system memory is structured

within code buffers. Each code buffer may contain a com-

pressed field or a frame (2 fields), in accordance with a user

configurable register bit.

The ZR36067 supports four code buffers, defined dynamically in

a dedicated table (the Code Buffer Table) in the system memory.

The actual memory of each code buffer may be fragmented. The

content of each entry in the code buffer table is a pointer to a

secondary Fragment Table. The fragment table contains the

pointers to the allocated memory chunks (fragments).

In JPEG Compression mode, the host software builds and

updates the code buffer table and the fragment tables according

the memory allocated by the operating system. On every JPEG

field/frame process, the ZR36067 Code DMA Controller reads

the fragment table pointer of the current buffer from the code

buffer table, and then fills up the buffer fragments one by one.

In JPEG Decompression mode, the host software builds the

code buffer table and fragment tables, and fills the fragments

with the compressed field or frame. On every JPEG process, the

ZR36067 Code DMA Controller retrieves the code fragments

one by one, and directs them to the Codec bus.

5.0 INTERFACES

5.1 PCI Bus Interface

In general, the ZR36067 is compatible with the PCI 2.1 specifi-

cations. As a bus master, it may initiate two types of data transfer

over the PCI bus:

• Memory Write (PCI command 0111b), from the ZR36067’s

Video FIFO buffer to the display memory (or main memory),

and from ZR36067’s Code FIFO buffer to the system

memory.

• Memory Read Line (PCI command 1110b), from system

memory to the ZR36067’s Mask Buffer[1] and from system

memory to the ZR36067’s Code FIFO buffer.

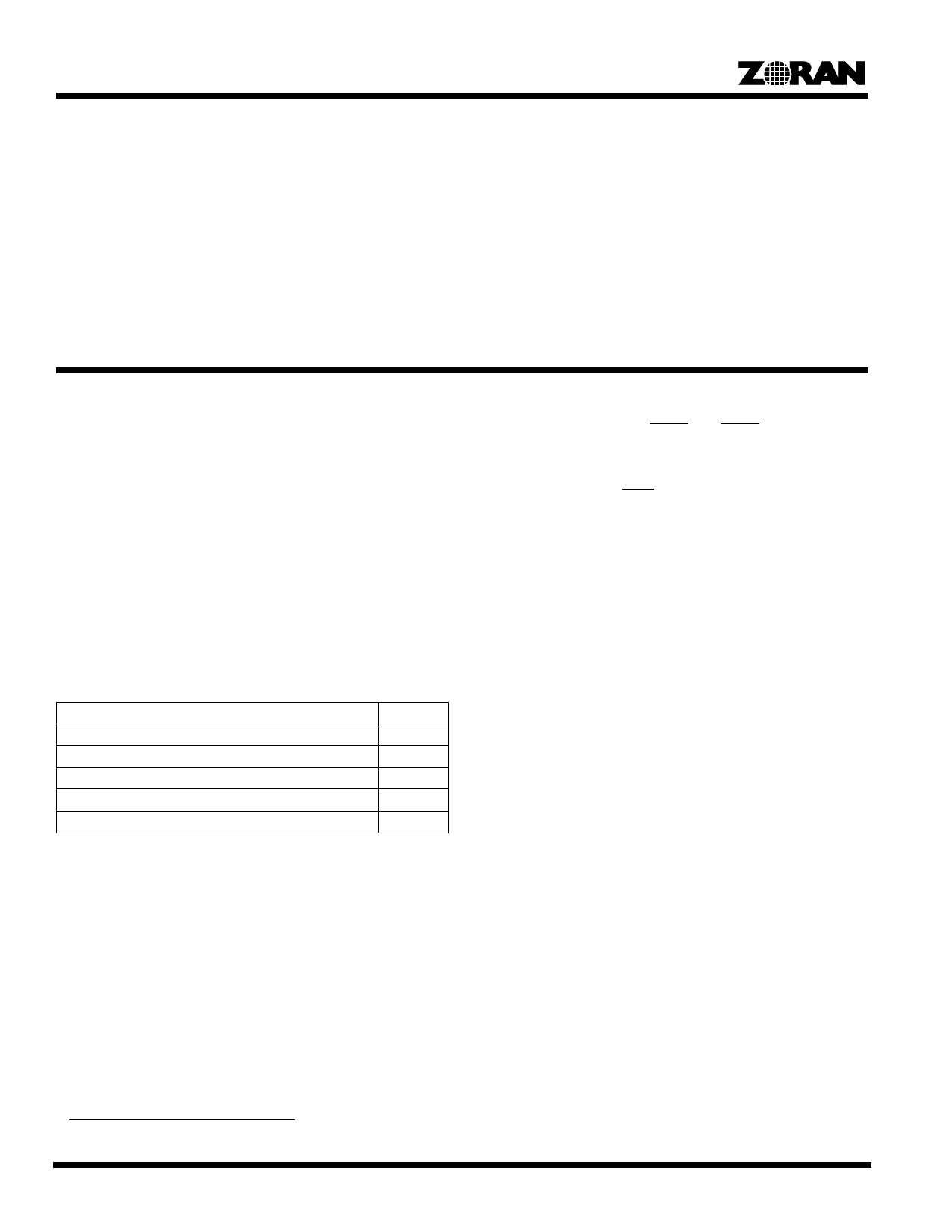

As a bus target, the ZR36067 responds to the following types of

transfer:

Memory Read

Memory Read Line

Memory Read Multiple

Memory Write

Configuration Read

Configuration Write

(0110b)

(1110b)

(1100b)

(0111b)

(1010b)

(1011b)

All other PCI commands are ignored.

Memory Read Line and Memory Read Multiple are handled

exactly like Memory Read.

Normally, as a slave, the ZR36067 is intended to be accessed

with single data phase cycles. However, multiple phase bursts

are supported. When the ZR36067 is accessed in a burst it

increments its internal (offset) address such that each data

phase is routed to/from the next address location (in double-

words). The ZR36067 supports byte enables, such that an

access to explicit bytes is possible.

The error reporting signals, SERR and PERR, are not included

in the ZR36067: as a multimedia device it is only required to

report parity errors through the PCI status register.

The ZR36067 uses the INTA PCI interrupt request line.

5.2 Digital Video Interface

The ZR36067 interfaces to a wide spectrum of digital video

devices. The Video Interface is bidirectional and two video pixel

flows are supported:

• The incoming video is sampled and directed via the

ZR36067’s video input processor to the graphics display

memory or system memory.

• The video pixels are transferred to or from the system mem-

ory using a dedicated mechanism (the Still Transfer

mechanism).

The ZR36067 supports two sync signal source configuration

options:

• External sync - the sync signals are driven by the external

video source.

• Internal sync - the sync signals are generated internally and

mastered by the ZR36067.

In JPEG Motion Video Compression and Decompression modes

as well as in MPEG mode, the Video Interface transfers the

incoming video to the ZR36067’s video input processor. The

sampling of the video stream is performed according to the video

clocks and sync signals. In JPEG Motion Video Compression

mode and in MPEG mode, the synchronization source should be

external. In JPEG Motion Video Decompression mode, the syn-

chronization source can be either external or internal.

In JPEG Still Image Compression and Decompression modes,

the ZR36067 uses a dedicated mechanism (the Still Transfer

mechanism) as a means for the host software to transfer pixels

to or from the compression module. The Video Interface masters

1. Not shown in the block diagram.

10