PDI1394L21 データシートの表示(PDF) - Philips Electronics

部品番号

コンポーネント説明

一致するリスト

PDI1394L21 Datasheet PDF : 52 Pages

| |||

Philips Semiconductors

1394 full duplex AV link layer controller

Preliminary specification

PDI1394L21

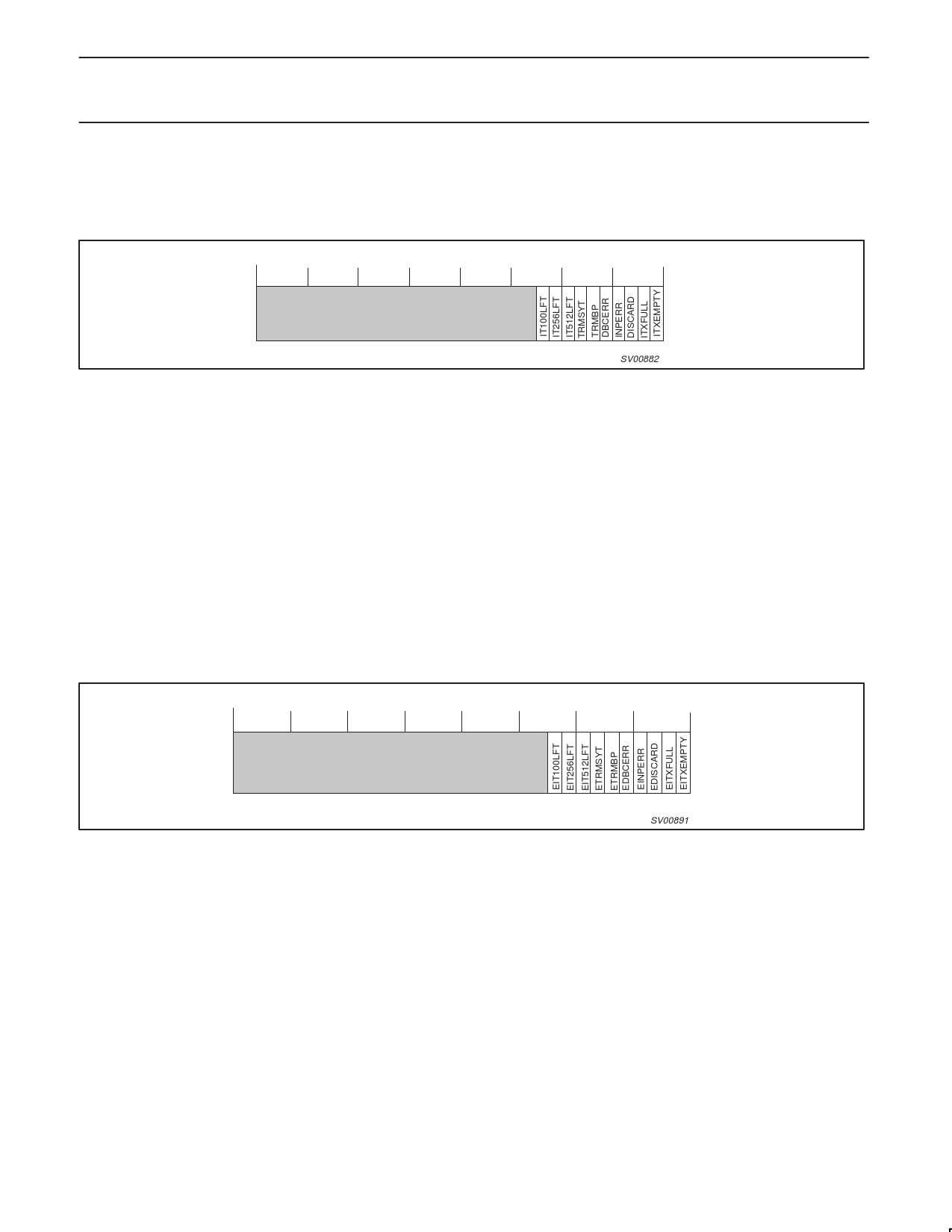

13.2.4 Isochronous Transmitter Interrupt Acknowledge (ITXINTACK) – Base Address: 0x02C

The AV Transmitter Interrupt Control and Status register is the interrupt register for the AV transmitter.

Bits 2, 3, and 4 ”auto repair” themselves, i.e. AVLINK will detect the situation and attempt to recover on its own. The host controller still needs to

clear these interrupts to be alerted the next time.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SV00882

Reset Value 0x00000000

Bits 9 .. 0 are interrupt acknowledge bits; and are defined as:

Bit 9:

R/W IT100LFT: Interrupt when transmitter queue reaches 100 quadlets from full. (924 of 1024 quadlets in queue)

Bit 8:

R/W IT256LFT: Interrupt when transmitter queue reaches 256 quadlets from full. (768 of 1024 quadlets in queue)

Bit 7:

R/W IT512LFT: Interrupt when transmitter queue reaches 50% of full. (512 of 1024 quadlets in queue)

Bit 6:

R/W TRMSYT: Interrupt on transmission of a SYT in CIP header quadlet 2

Bit 5:

R/W TRMBP: Interrupt on payload transmission/discard complete.

Bit 4:

R/W DBCERR: Acknowledge interrupt on Data Block Count (DBC) synchronization loss.

Bit 3:

R/W INPERR: Acknowledge interrupt on input error (input data discarded).

Bit 2:

R/W DISCARD: Interrupt on lost cycle (payload discarded).

Bit 1:

R/W ITXFULL: Interrupt on isochronous memory bank full. This is a fatal error, the recommended action is to reset and

re-initialize the transmitter.

Bit 0:

R/W ITXEMPTY: Interrupt on isochronous memory bank empty.

Other bits will always read ‘0’.

13.2.5 Isochronous Transmitter Interrupt Enable (ITXINTE) – Base Address: 0x030

These are the enabled bits for the AV Transmitter Control.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SV00891

Reset Value 0x00000000

Bits 9..0 are interrupt enable bits for the Isochronous Transmitter Interrupt Acknowledge register (ITXINTACK).

1999 Aug 06

35