NM34C02 データシートの表示(PDF) - Fairchild Semiconductor

部品番号

コンポーネント説明

一致するリスト

NM34C02 Datasheet PDF : 12 Pages

| |||

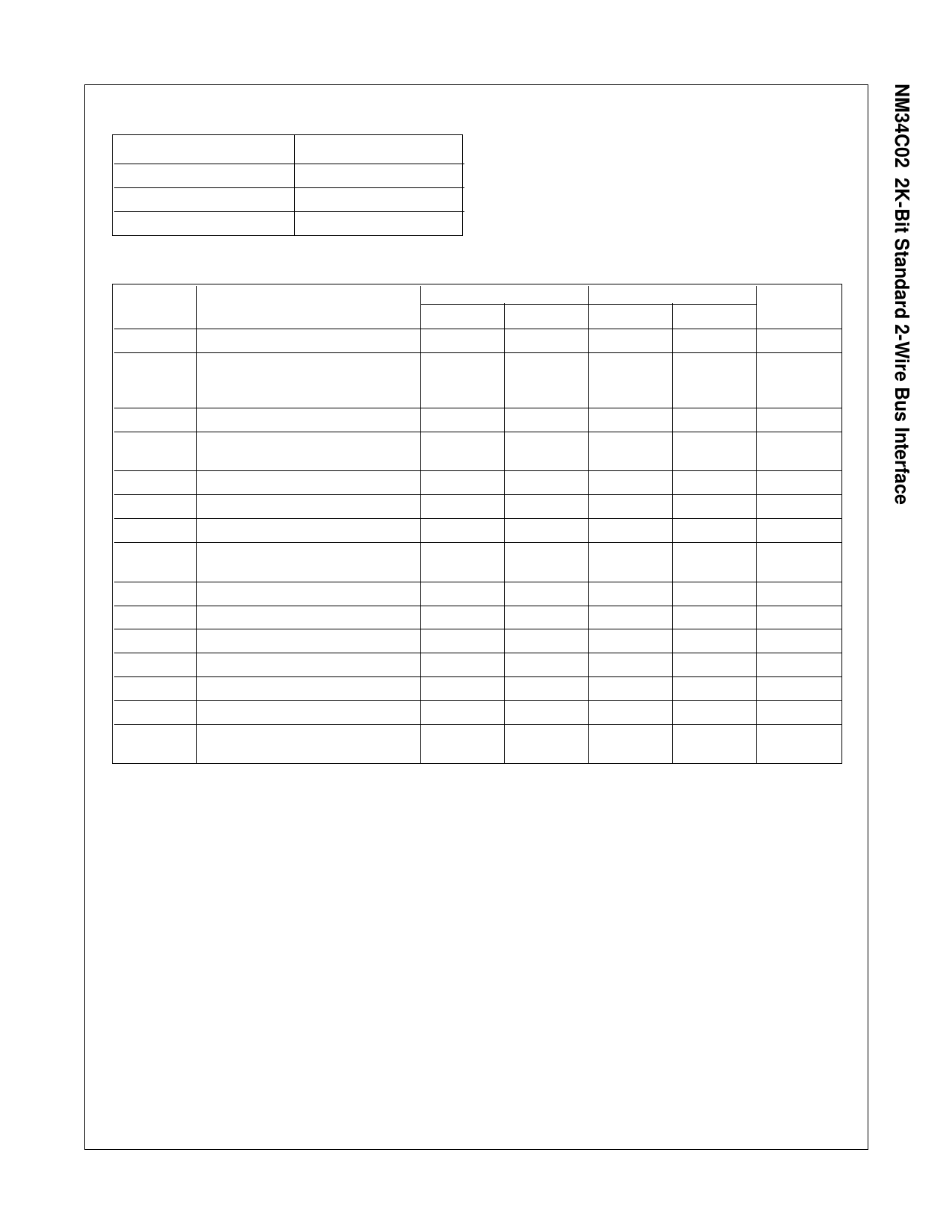

AC Conditions of Test

Input Pulse Levels

Input Rise and Fall Times

VCC x 0.1 to VCC x 0.9

10 ns

Input & Output Timing Levels VCC x 0.5

Output Load

1 TTL Gate and CL = 100 pF

Read and Write Cycle Limits (Standard and Low VCC Range 2.7V - 4.5V)

Symbol

Parameter

100 KHz

Min

Max

400 KHz

Min

Max

fSCL

SCL Clock Frequency

100

400

TI

Noise Suppression Time Constant at

SCL, SDA Inputs (Minimum VIN

100

50

Pulse width)

tAA

SCL Low to SDA Data Out Valid

0.3

3.5

0.1

0.9

tBUF

Time the Bus Must Be Free before

4.7

1.3

a New Transmission Can Start

tHD:STA

Start Condition Hold Time

4.0

0.6

tLOW

Clock Low Period

4.7

1.5

tHIGH

Clock High Period

4.0

0.6

tSU:STA

Start Condition Setup Time

4.7

0.6

(for a Repeated Start Condition)

tHD:DAT

tSU:DAT

tR

tF

tSU:STO

tDH

tWR

(Note 3)

Data in Hold Time

Data in Setup Time

SDA and SCL Rise Time

SDA and SCL Fall Time

Stop Condition Setup Time

Data Out Hold Time

Write Cycle Time - NM34C02

- NM34C02L, NM34C02LZ

0

0

250

100

1

0.3

300

300

4.7

0.6

300

50

10

10

15

15

Units

KHz

ns

µs

µs

µs

µs

µs

µs

µs

ns

µs

ns

µs

ns

ms

Note 3: The write cycle time (tWR) is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle. During the write cycle, the

NM34C02 bus interface circuits are disabled, SDA is allowed to remain high per the bus-level pull-up resistor, and the device does not respond to its slave address.

NM34C02 Rev. D.2

4

www.fairchildsemi.com