ADSP-2191MKCA-160 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

一致するリスト

ADSP-2191MKCA-160 Datasheet PDF : 52 Pages

| |||

ADSP-2191M

All DMA transfers use the DMA bus shown in the functional

block diagram on page 1. Because all of the peripherals use the

same bus, arbitration for DMA bus access is needed. The arbi-

tration for DMA bus access appears in Table 4.

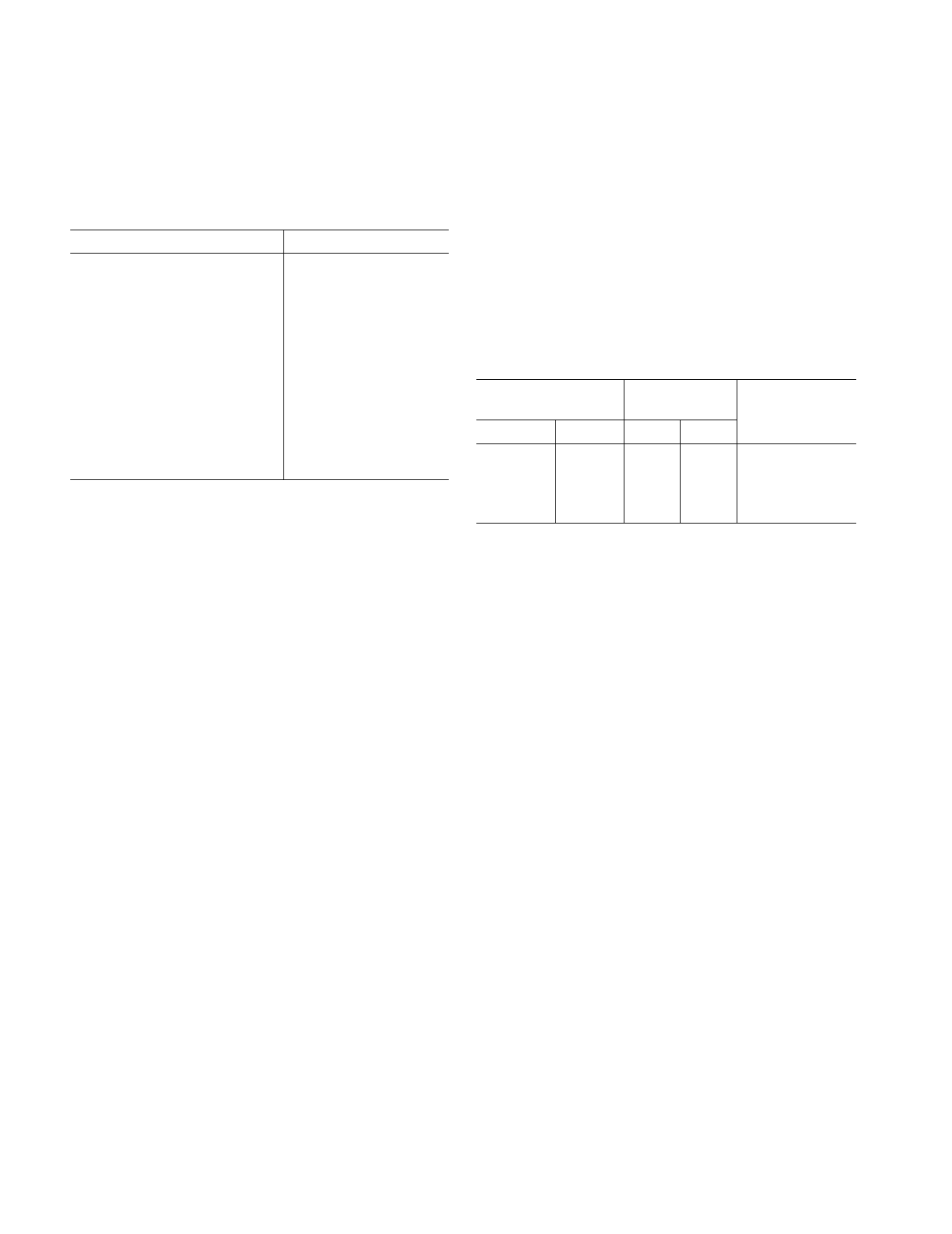

Table 4. I/O Bus Arbitration Priority

DMA Bus Master

SPORT0 Receive DMA

SPORT1 Receive DMA

SPORT2 Receive DMA

SPORT0 Transmit DMA

SPORT1 Transmit DMA

SPORT2 Transmit DMA

SPI0 Receive/Transmit DMA

SPI1 Receive/Transmit DMA

UART Receive DMA

UART Transmit DMA

Host Port DMA

Memory DMA

Arbitration Priority

0—Highest

1

2

3

4

5

6

7

8

9

10

11—Lowest

Host Port

The ADSP-2191M’s Host port functions as a slave on the

external bus of an external Host. The Host port interface lets a

Host read from or write to the DSP’s memory space, boot space,

or internal I/O space. Examples of Hosts include external micro-

controllers, microprocessors, or ASICs.

The Host port is a multiplexed address and data bus that provides

both an 8-bit and a 16-bit data path and operates using an asyn-

chronous transmission protocol. Through this port, an off-chip

Host can directly access the DSP’s entire memory space map,

boot memory space, and internal I/O space. To access the DSP’s

internal memory space, a Host steals one cycle per access from

the DSP. A Host access to the DSP’s external memory uses the

external port interface and does not stall (or steal cycles from)

the DSP’s core. Because a Host can access internal I/O memory

space, a Host can control any of the DSP’s I/O mapped

peripherals.

The Host port is most efficient when using the DSP as a slave

and uses DMA to automate the incrementing of addresses for

these accesses. In this case, an address does not have to be trans-

ferred from the Host for every data transfer.

Host Port Acknowledge (HACK) Modes

The Host port supports a number of modes (or protocols) for

generating a HACK output for the host. The host selects ACK

or Ready Modes using the HACK_P and HACK pins. The Host

port also supports two modes for address control: Address Latch

Enable (ALE) and Address Cycle Control (ACC) modes. The

DSP auto-detects ALE versus ACC Mode from the HALE and

HWR inputs.

The Host port HACK signal polarity is selected (only at reset) as

active high or active low, depending on the value driven on the

HACK_P pin.The HACK polarity is stored into the Host port

configuration register as a read only bit.

The DSP uses HACK to indicate to the Host when to complete

an access. For a read transaction, a Host can proceed and

complete an access when valid data is present in the read buffer

and the Host port is not busy doing a write. For a write transac-

tions, a Host can complete an access when the write buffer is not

full and the Host port is not busy doing a write.

Two mode bits in the Host Port configuration register HPCR

[7:6] define the functionality of the HACK line. HPCR6 is ini-

tialized at reset based on the values driven on HACK and

HACK_P pins (shown in Table 5); HPCR7 is always cleared (0)

at reset. HPCR [7:6] can be modified after reset by a write access

to the Host port configuration register.

Table 5. Host Port Acknowledge Mode Selection

Values Driven At

Reset

HACK_P HACK

0

0

0

1

1

0

1

1

HPCR [7:6]

Initial Values

Bit 7 Bit 6

0

1

0

0

0

0

0

1

Acknowledge

Mode

Ready Mode

ACK Mode

ACK Mode

Ready Mode

The functional modes selected by HPCR [7:6] are as follows

(assuming active high signal):

• ACK Mode—Acknowledge is active on strobes; HACK

goes high from the leading edge of the strobe to indicate

when the access can complete. After the Host samples the

HACK active, it can complete the access by removing the

strobe.The Host port then removes the HACK.

• Ready Mode—Ready active on strobes, goes low to insert

waitstate during the access.If the Host port cannot

complete the access, it deasserts the HACK/READY line.

In this case, the Host has to extend the access by keeping

the strobe asserted. When the Host samples the HACK

asserted, it can then proceed and complete the access by

deasserting the strobe.

While in Address Cycle Control (ACC) mode and the ACK or

Ready acknowledge modes, the HACK is returned active for any

address cycle.

Host Port Chip Selects

There are two chip-select signals associated with the Host port:

HCMS and HCIOMS. The Host Chip Memory Select (HCMS)

lets the Host select the DSP and directly access the DSP’s inter-

nal/external memory space or boot memory space. The Host

Chip I/O Memory Select (HCIOMS) lets the Host select the DSP

and directly access the DSP’s internal I/O memory space.

Before starting a direct access, the Host configures Host port

interface registers, specifying the width of external data bus

(8- or 16-bit) and the target address page (in the IJPG register).

The DSP generates the needed memory select signals during the

access, based on the target address. The Host port interface

combines the data from one, two, or three consecutive Host

accesses (up to one 24-bit value) into a single DMA bus access

to prefetch Host direct reads or to post direct writes. During

assembly of larger words, the Host port interface asserts ACK for

–8–

REV. 0