IMIC9835 データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

一致するリスト

IMIC9835

IMIC9835 Datasheet PDF : 18 Pages

| |||

C9835

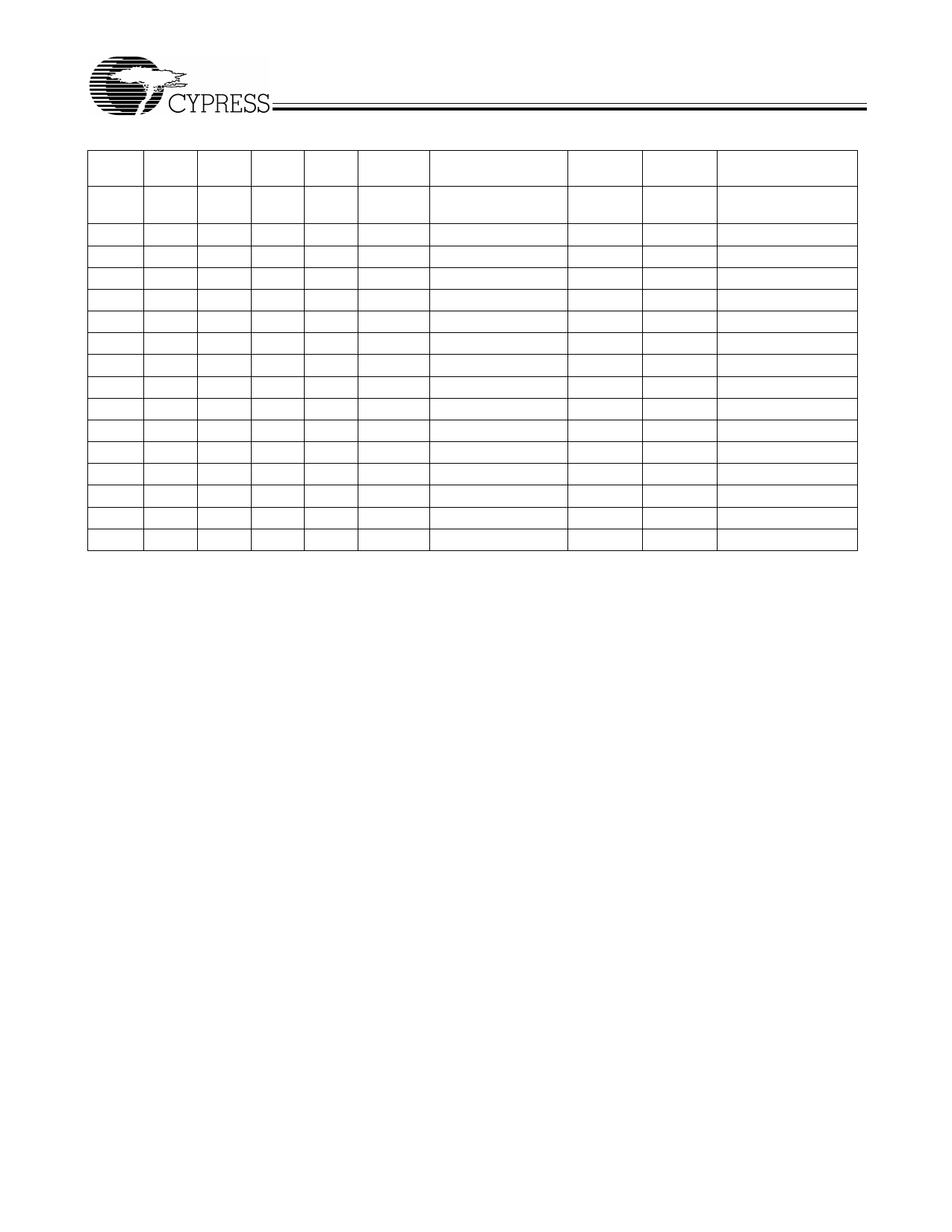

Table 2. Expanded Frequency Selection (MHz)[4, 5, 6]

TEST# ESEL ESEL SEL

1

0

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

0

1

1

1

0

0

1

0

0

1

0

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

SEL CPU(0:2)

0

66.7

1

100

0

133.3

1

133.3

0

70

1

105

0

140

1

140

0

73.3

1

110

0

146.7

1

146.7

0

80

1

120

0

160

1

160

SDRAM(0:5),

DCLK

100[6]

100[6]

133.3

100[6]

105[6]

105[6]

140

105[6]

110[6]

110[6]

146.7

110[6]

120[6]

120[6]

160

120[6]

PCI_F,

3V66(0:2) PCI(1:6)

66.6

33

66.6

33

66.6

33

66.6

33

70

35

70

35

70

35

70

35

73.3

36.6

73.3

36.6

73.3

36.6

73.3

36.6

80

40

80

40

80

40

80

40

Notes

0% extension

(Default)

5% extension

10% extension

20% extension

Power Management Functions

Power management on this device is controlled by the PD#,

CPU_STP# and PCI_STP# pins. When PD# is high (default)

the device is in normal running mode and all signals are active.

The PD# signal is used to bring all clocks to a low level in an

orderly fashion prior to power (all except AVDD) being

removed from the part. When PD# is asserted (forced) low, the

device transitions to a shutdown (power down) mode and all

power supplies (3.3V and 2.5V except for AVDD) may then be

removed. When PD# is sampled low by two consecutive rising

edges of the CPU clock, then all affected clocks are stopped

in a low state on their next high-to-low transition. The REF and

USB clocks are stopped in a low state as soon as possible.

When in power down (and before power is removed), all

outputs are synchronously stopped in a low state (see

Figure 1), all PLLs are shut off, and the crystal oscillator is

disabled. When the device is shutdown, the I²C function is

also disabled.

At power-up, using the PD# select pin, all clocks are started in

such a manner as to guarantee a glitch-free operation, no

partial clock pulses.

Notes:

4. Extended frequencies are only available via SMBUS interface. They are accessable via SMBUS Byte 5 bits 0,1.

5. 48M(0,1) clocks are constant at 48 MHz and REF is constant at 14.31818 MHz for all table selections.

6. Will be set to 133 MHz and boosted accordingly, when Byte3,Bit 0 is set to logic 1.

Document #: 38-07303 Rev. **

Page 3 of 18