ISP1561 データシートの表示(PDF) - Philips Electronics

部品番号

コンポーネント説明

一致するリスト

ISP1561 Datasheet PDF : 102 Pages

| |||

Philips Semiconductors

ISP1561

USB PCI host controller

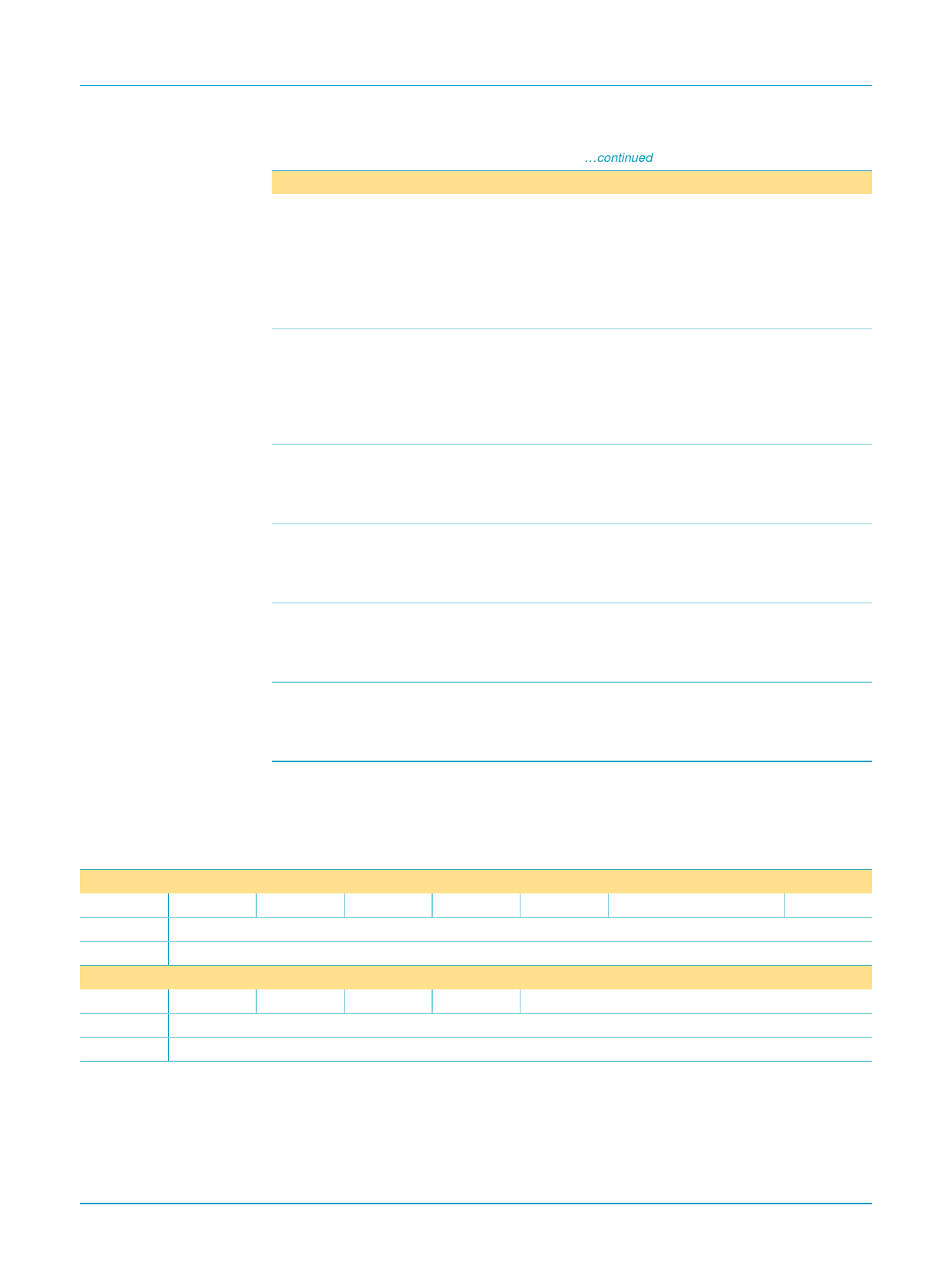

Table 7:

Bit

5

4

3

2

1

0

Command register: bit description…continued

Symbol Description

VGAPS

VGA Palette Snoop: This bit controls how VGA compatible and

graphics devices handle accesses to VGA palette registers. When

this bit is logic 1, palette snooping is enabled (that is, the device

does not respond to palette register writes and snoops the data).

When the bit is logic 0, the device should treat palette write

accesses like all other accesses. VGA compatible devices should

implement this bit.

MWIE

Memory Write and Invalidate Enable: This is an enable bit for

using the Memory Write and Invalidate command. When this bit is

logic 1, masters may generate the command. When it is logic 0,

Memory Writes must be used instead. State after RST# is logic 0.

This bit must be implemented by master devices that can generate

the Memory Write and Invalidate command.

SC

Special Cycles: Controls the action of a device on Special Cycle

operations. A value of logic 0 causes the device to ignore all

Special Cycle operations. A value of logic 1 allows the device to

monitor Special Cycle operations. State after RST# is logic 0.

BM

Bus Master: Controls the ability of a device to act as a master on

the PCI bus. A value of logic 0 disables the device from generating

PCI accesses. A value of logic 1 allows the device to behave as a

bus master. State after RST# is logic 0.

MS

Memory Space: Controls the response of a device to Memory

Space accesses. A value of logic 0 disables the device response.

A value of logic 1 allows the device to respond to Memory Space

accesses. State after RST# is logic 0.

IOS

IO Space: Controls the response of a device to I/O Space

accesses. A value of logic 0 disables the device response. A value

of logic 1 allows the device to respond to I/O Space accesses.

State after RST# is logic 0.

Status register (address: 06H): The Status register is a two-byte read-only register

used to record status information on PCI bus-related events (bit allocation: see

Table 8).

Table 8: Status register: bit allocation

Bit

15

14

13

12

11

Symbol

DPE

SSE

RMA

RTA

STA

Reset

0

0

0

0

0

Access

R

R

R

R

R

Bit

7

6

5

4

3

Symbol

FBBC

reserved

66MC

CL

Reset

0

0

0

1

0

Access

R

-

R

R

-

10

9

DEVSELT[1:0]

0

1

R

R

2

1

reserved

0

0

-

-

8

MDPE

0

R

0

0

-

9397 750 10015

Product data

Rev. 01 — 06 February 2003

© Koninklijke Philips Electronics N.V. 2003. All rights reserved.

18 of 102