IDT82V2048(2010) データシートの表示(PDF) - Integrated Device Technology

部品番号

コンポーネント説明

一致するリスト

IDT82V2048 Datasheet PDF : 62 Pages

| |||

IDT82V2048 OCTAL T1/E1 SHORT HAUL LINE INTERFACE UNIT

INDUSTRIAL TEMPERATURE RANGES

Table-1 Pin Description (Continued)

Name

Pin No.

Type

TQFP144 PBGA160

Description

MCn: Performance Monitor Configuration 3~0

In hardware control mode, A4 must be connected to GND. MC[3:0] are used to select one transmitter or

receiver of channel 1 to 7 for non-intrusive monitoring. Channel 0 is used as the monitoring channel. If a

transmitter is monitored, signals on the corresponding pins TTIPn and TRINGn are internally transmitted

to RTIP0 and RRING0. If a receiver is monitored, signals on the corresponding pins RTIPn and RRINGn

are internally transmitted to RTIP0 and RRING0. The monitored is then output to RDP0 and RDN0 pins.

In host mode operation, the signals monitored by channel 0 can be routed to TTIP0/RING0 by activating

the remote loopback in this channel. Refer to 2.20 G.772 Monitoring for more details.

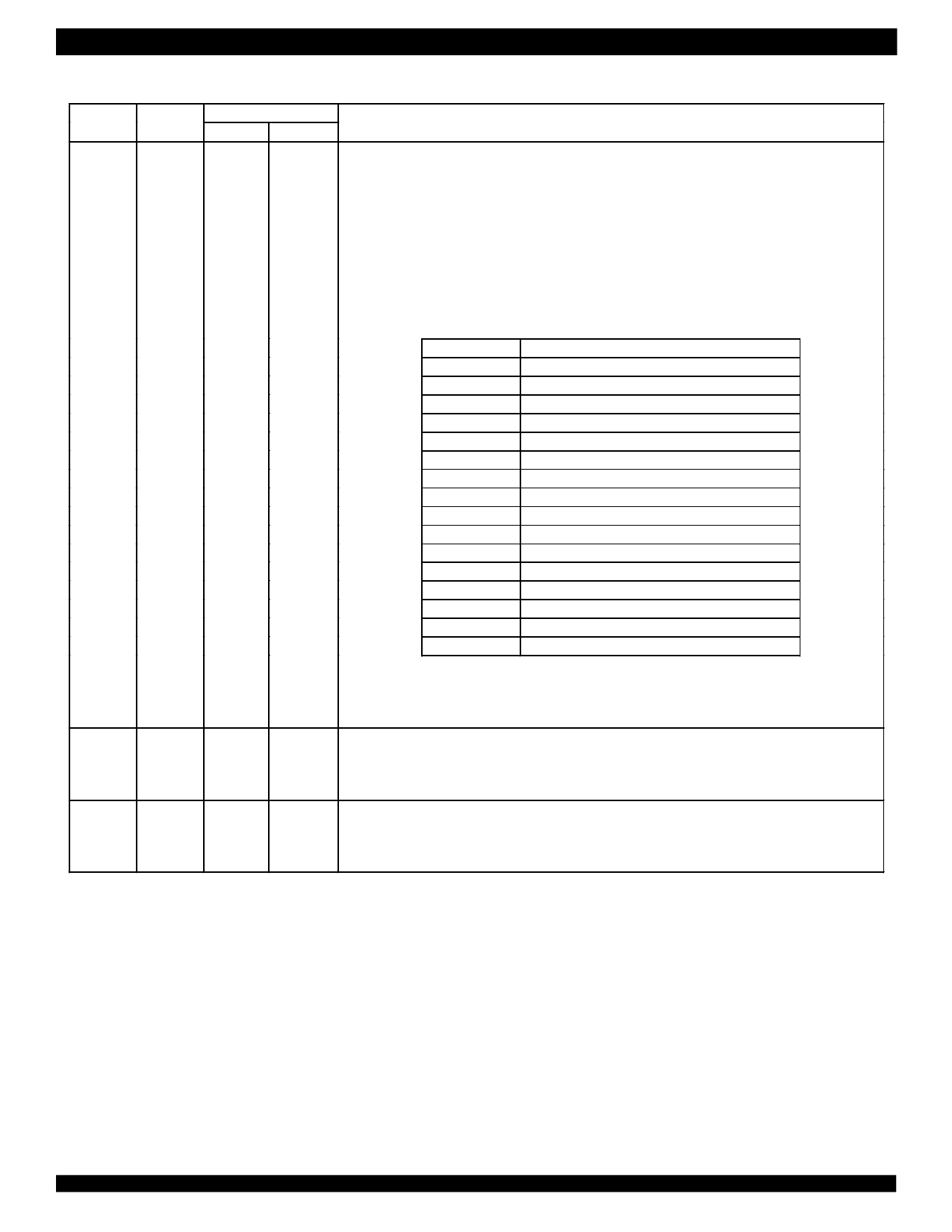

Performance Monitor Configuration determined by MC[3:0] is shown below. Note that if MC[2:0] = 000, the

device is in normal operation of all the channels.

A4

12

F4

MC3/A3

13

F3

MC2/A2

I

14

F2

MC1/A1

15

F1

MC0/A0

16

G3

MC[3:0]

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Monitoring Configuration

Normal operation without monitoring

Monitor Receiver 1

Monitor Receiver 2

Monitor Receiver 3

Monitor Receiver 4

Monitor Receiver 5

Monitor Receiver 6

Monitor Receiver 7

Normal operation without monitoring

Monitor Transmitter 1

Monitor Transmitter 2

Monitor Transmitter 3

Monitor Transmitter 4

Monitor Transmitter 5

Monitor Transmitter 6

Monitor Transmitter 7

OE

CLKE

TRST

TMS

TCK

I

114

I

115

I

95

Pull-up

I

96

Pull-up

I

97

An: Address Bus 4~0

When pin MODE1 is low, the parallel host interface operates with separate address and data bus. In this

mode, the signal on this pin is the address bus of the host interface.

OE: Output Driver Enable

E14 Pulling this pin low can drive all driver output into high-Z for redundancy application without external

mechanical relays. In this condition, all other internal circuits remain active.

CLKE: Clock Edge Select

E13

The signal on this pin determines the active edge of RCLKn and SCLK in clock recovery mode, or deter-

mines the active level of RDPn and RDNn in the data recovery mode. See 2.3 Clock Edges on page 14 for

details.

JTAG Signals

TRST: JTAG Test Port Reset (Active Low)

G12 This is the active low asynchronous reset to the JTAG Test Port. This pin has an internal pull-up resistor

and it can be left open.

TMS: JTAG Test Mode Select

F11 The signal on this pin controls the JTAG test performance and is clocked into the device on the rising

edges of TCK. This pin has an internal pull-up resistor and it can be left open.

TCK: JTAG Test Clock

F14

This pin input the clock of the JTAG Test. The data on TDI and TMS are clocked into the device on the ris-

ing edges of TCK, while the data on TDO is clocked out of the device on the falling edges of TCK. This pin

should be connected to GNDIO or VDDIO pin when unused.

10