CDB6403 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

一致するリスト

CDB6403 Datasheet PDF : 54 Pages

| |||

CS6403

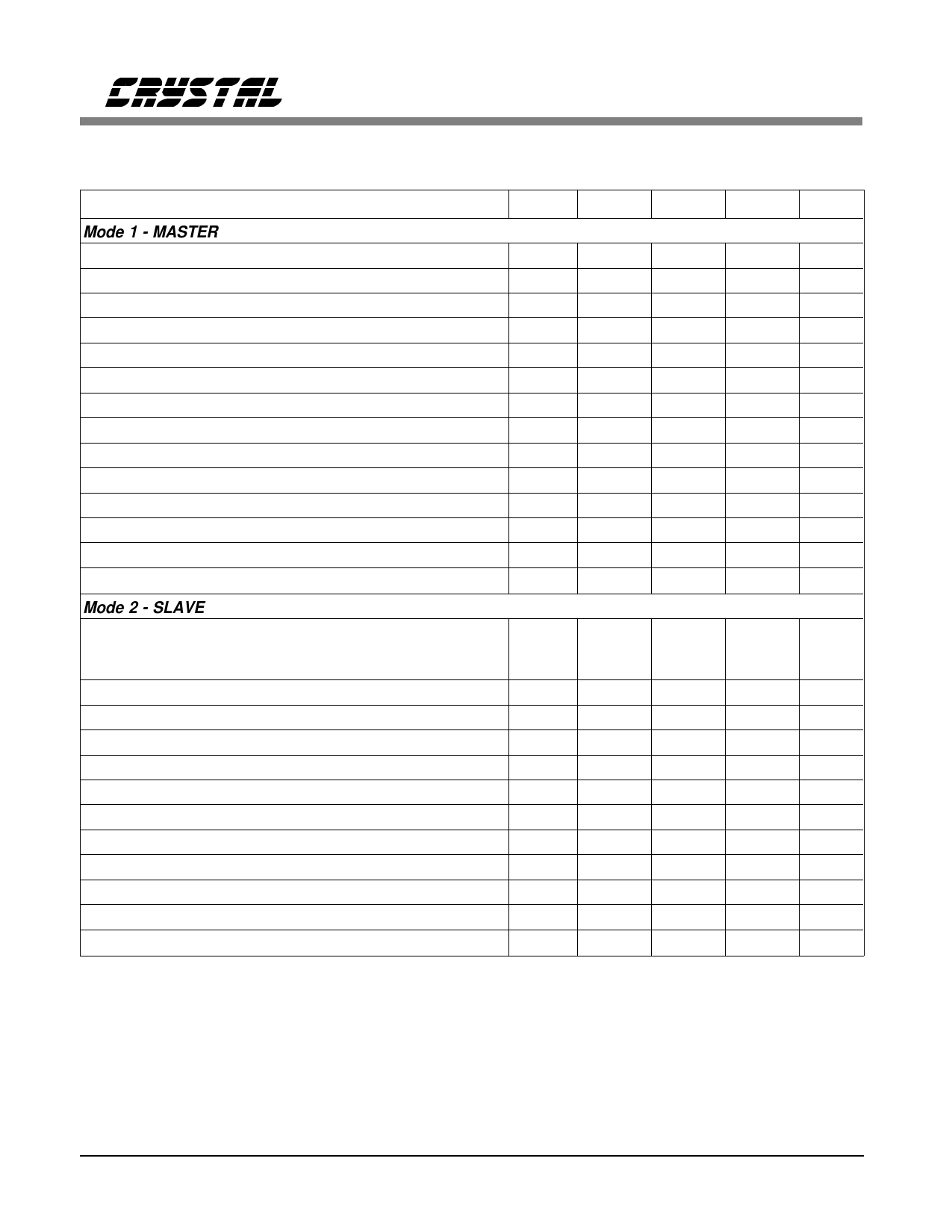

SWITCHING CHARACTERISTICS (TA = 25°C; AVDD and DVDD = +5V, output loaded with

30 pF; Input Levels: Logic 0 = 0V, Logic 1 = DVDD)

Parameter

Symbol Min

Typ

Max Units

Mode 1 - MASTER

Input clock (CLKIN) frequency

CLKIN 7.78 8.192 8.60 MHz

CLKIN low time

CLKIN high time

Sample Rate

tckl

30

-

tckh

30

-

Fs

-

8

-

ns

-

ns

-

kHz

SCLK and SYNCOUT output delay from CLKIN rising

tpd3

-

-

SCLK duty cycle

(Note 12) tsckw

-

50

SCLK rising to SYNCOUT rising

tsr1

-

12

SCLK rising to SYNCOUT falling

tsf1

-

6

SDO delay from SCLK edge

tpd1

-

-

SDI setup time to SCLK edge

ts1

15

-

SDI hold time from SCLK edge

th1

10

-

SDO to Hi-Z state

thz

-

-

SDO to non-Hi-Z

bit 1

tnz

5

-

RESET pulse width high

250

-

Mode 2 - SLAVE

50

ns

-

%

30

ns

30

ns

70

ns

-

ns

-

ns

50

ns

-

ns

-

µs

Input clock (SCLK) frequency

SCLK 243

256

268

kHz

0.97 1.024 1.08 MHz

1.95 2.048 2.15 MHz

SCLK low time

SCLK high time

SYNCOUT output delay from SSYNC rising

SYNCOUT output delay from SSYNC falling

Sample Rate

tckl

150

-

tckh

150

-

tpdsr

-

-

tpdsf

-

-

Fs

-

8

-

ns

-

ns

50

ns

50

ns

-

kHz

SDI/SSYNC setup time to SCLK edge

ts1

15

-

-

ns

SDI/SSYNC hold time from SCLK edge

th1

10

-

-

ns

SDO delay from SCLK edge

tpd1

-

-

70

ns

SDO to Hi-Z state

bit 16/8

thz

-

-

50

ns

SDO to non-Hi-Z

bit 1

tnz

5

-

-

ns

RESET pulse width high

250

-

-

µs

Notes: 12. When the CS6403 is in master mode (SSYNC and SCLK outputs), the SCLK duty cycle is 50%.

The period of SCLK is 4/CLKIN.

6

DS192PP6