CDB6403 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

一致するリスト

CDB6403 Datasheet PDF : 54 Pages

| |||

CS6403

Analog Interface

The codec block provides an analog-to-digital

converter (ADC) and a digital-to-analog con-

verter that can be connected directly to a

microphone and a speaker, respectively.

The output of the microphone should be low-

pass filtered, then AC-coupled to the audio input,

MICIN. A 26 dB gain stage is included in the

CS6403 at the ADC input to amplify the micro-

phone signal. However, this gain stage may be

bypassed in modes in which a line-level source

is connected to the CS6403 instead of a micro-

phone. The CS6403 also includes a speaker

driver, which can drive an 8Ω speaker directly,

or alternatively, it can drive a high-impedance

differential input on an external amplifier.

With the 26 dB gain stage on, the fullscale input

for the MICIN pin is 100mV peak-to-peak. Any

signal over 100mV peak-to-peak will clip the in-

put to the ADC. With the gain stage off, a 2V

peak-to-peak signal is the maximum allowed.

The fullscale output voltage from the DAC is

1.75V peak-to-peak single-ended, or 3.5V peak-

to-peak differentially.

SCLK

000

001

010

011

100

101

110

111

Clock Rate I/O

256 kHz I

undefined

1.024 MHz I

2.048 MHz I

mode

slave

slave

slave

undefined

undefined

undefined

2.048 MHz O master

It is very important to not clip signals anywhere

in the system. An echo canceller can only re-

move echo that passes through a linear, time

invariant path. Echo that passes through a non-

linearity (like clipping) will not be removed by

the echo canceller.

Both the DAC and ADC paths are bandlimited

as a function of sampling rate. At a sampling

rate of 8 kHz, the paths are limited to 0-

3600 Hz.

Synchronous Serial Interface

The Synchronous Serial Interface (SSI) provides

a data and control interface to the CS6403. The

SSI can be connected to an external network

codec for applications like speakerphones or to a

DSP for high-end applications like video tele-

conferencing.

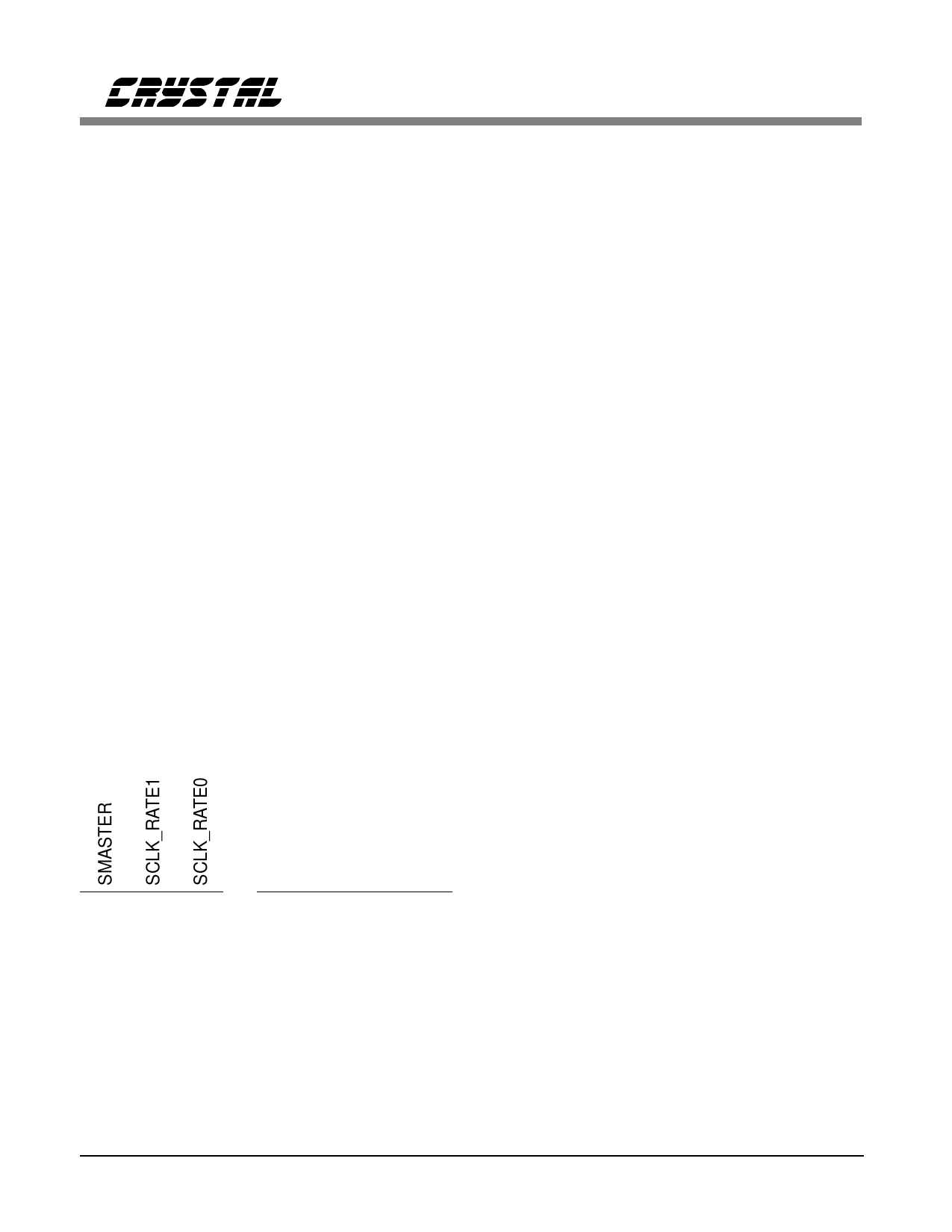

Depending on the state of the SMASTER

(PIN 42Q, 4L) pin at RESET, the CS6403 can

operate as either a system timing master or slave.

As a master, the serial clock pin (SCLK) is an

output. As a system timing slave, SCLK must

be driven by an external source. When SMAS-

TER is high, the SCLK output frequency is a

fixed 2.048 MHz derived from the 8.192 MHz

crystal oscillator connected across CLKIN and

CLKOUT. When SMASTER is low, internal

timing is generated by the Phase Locked Loop

(PLL), which uses SCLK’s input as a timing ref-

erence, so no external crystal is necessary. In

slave timing mode, SCLK can be driven at 256

kHz, 1.024 MHz, or 2.048 MHz. The CS6403 is

informed of the SCLK rate via the

SCLK_RATE0 (PIN 29Q, 35L) and

SCLK_RATE1 (PIN 30Q, 36L) pins.

Table 1 shows the various options for SCLK.

Table 1. Clock Options

DS192PP6

11