EBD21RD4ABNA-10 データシートの表示(PDF) - Elpida Memory, Inc

部品番号

コンポーネント説明

一致するリスト

EBD21RD4ABNA-10 Datasheet PDF : 19 Pages

| |||

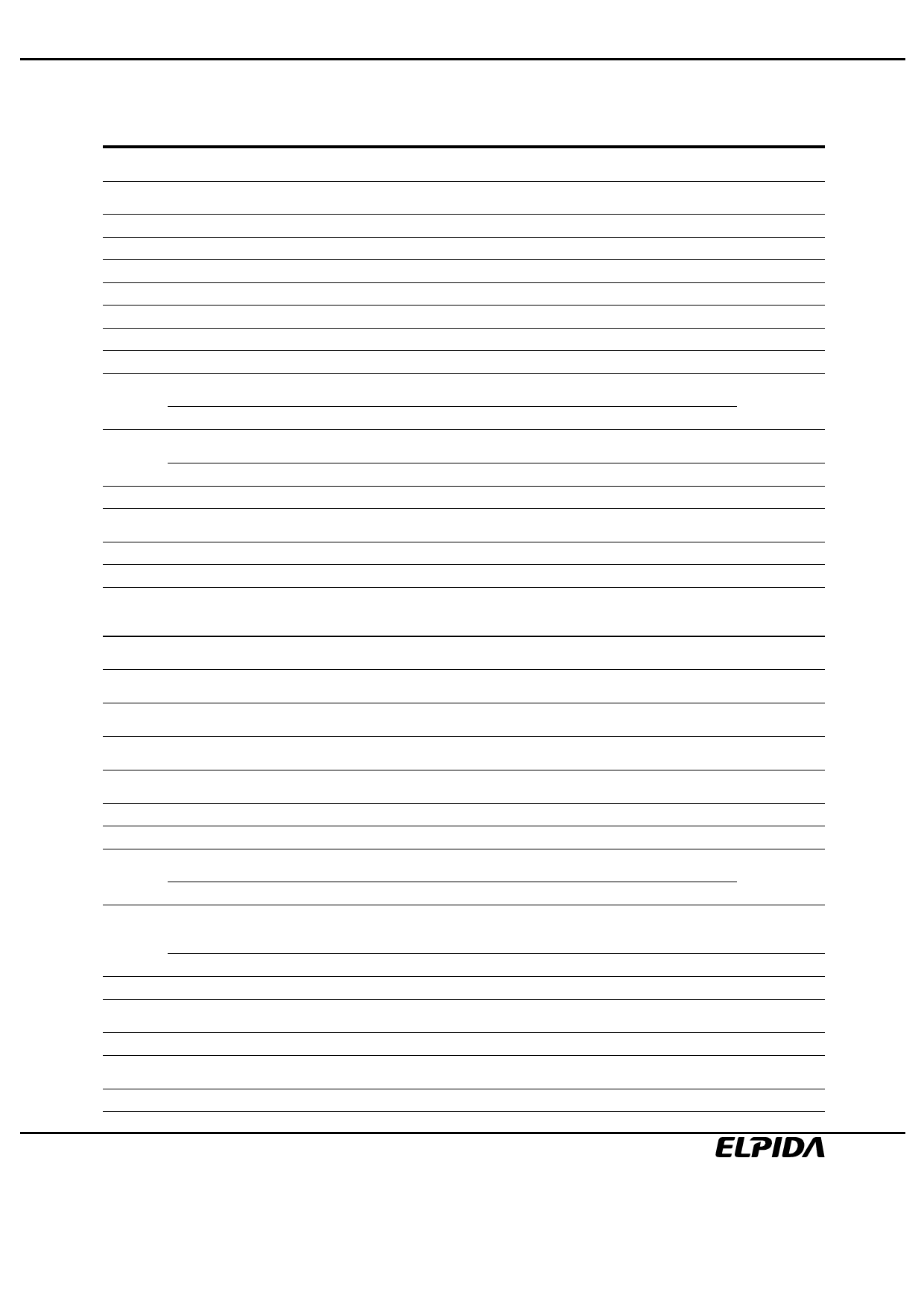

EBD21RD4ABNA

Serial PD Matrix*1

Byte No.

0

1

2

3

4

5

6

7

8

9

10

11

Function described

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Hex value

Number of bytes utilized by module

manufacturer

1

0

0

0

0

0

0

0

80H

Total number of bytes in serial PD

device

0 0 0 0 1 0 0 0 08H

Memory type

0 0 0 0 0 1 1 1 07H

Number of row address

0 0 0 0 1 1 0 1 0DH

Number of column address

0 0 0 0 1 1 0 0 0CH

Number of DIMM banks

0 0 0 0 0 0 1 0 02H

Module data width

0 1 0 0 1 0 0 0 48H

Module data width continuation

0 0 0 0 0 0 0 0 00H

Voltage interface level of this assembly 0 0 0 0 0 1 0 0 04H

DDR SDRAM cycle time, CL = X

-7A, -7B

0 1 1 1 0 1 0 1 75H

-10

1 0 1 0 0 0 0 0 A0H

SDRAM access from clock (tAC)

-7A, -7B

0 1 1 1 0 1 0 1 75H

-10

1 0 0 0 0 0 0 0 80H

DIMM configuration type

0 0 0 0 0 0 1 0 02H

12

Refresh rate/type

1 0 0 0 0 0 1 0 82H

13

Primary SDRAM width

0 0 0 0 0 1 0 0 04H

14

Error checking SDRAM width

0 0 0 0 0 1 0 0 04H

SDRAM device attributes:

15

Minimum clock delay back-to-back 0 0 0 0 0 0 0 1 01H

column access

16

SDRAM device attributes:

Burst length supported

0 0 0 0 1 1 1 0 0EH

17

SDRAM device attributes: Number of

banks on SDRAM device

0

0

0

0

0

1

0

0

04H

18

SDRAM device attributes:

/CAS latency

0 0 0 0 1 1 0 0 0CH

19

SDRAM device attributes:

/CS latency

0 0 0 0 0 0 0 1 01H

20

SDRAM device attributes:

/WE latency

0 0 0 0 0 0 1 0 02H

21

SDRAM module attributes

0 0 1 0 0 1 1 0 26H

22

SDRAM device attributes: General 1 1 0 0 0 0 0 0 C0H

23

Minimum clock cycle time at CLX - 0.5

-7A

0

1

1

1

0

1

0

1

75H

-7B, -10

1 0 1 0 0 0 0 0 A0H

Maximum data access time (tAC) from

24

clock at CLX - 0.5

0 1 1 1 0 1 0 1 75H

-7A, -7B

-10

1 0 0 0 0 0 0 0 80H

25

Minimum clock cycle time at CLX - 1 0 0 0 0 0 0 0 0 00H

26

Maximum data access time (tAC) from

clock at CLX - 1

0

0

0

0

0

0

0

0

00H

27

Minimum row precharge time (tRP) 0 1 0 1 0 0 0 0 50H

28

Minimum row active to row active

delay (tRRD)

0 0 1 1 1 1 0 0 3CH

29

Minimum /RAS to /CAS delay (tRCD) 0 1 0 1 0 0 0 0 50H

Comments

128

256 byte

SDRAM DDR

13

12

2

72 bits

0 (+)

SSTL 2.5V

CL = 2.5*3

0.75ns*3

0.8ns*3

ECC

7.8 µs

Self refresh

×4

×4

1 CLK

2, 4, 8

4

2, 2.5

0

1

Registered

± 0.2V

CL = 2*3

0.75ns*3

0.8ns*3

20ns

15ns

20ns

Preliminary Data Sheet E0273E20 (Ver. 2.0)

5