V54C3128404V データシートの表示(PDF) - Mosel Vitelic Corporation

部品番号

コンポーネント説明

一致するリスト

V54C3128404V Datasheet PDF : 45 Pages

| |||

MOSEL VITELIC

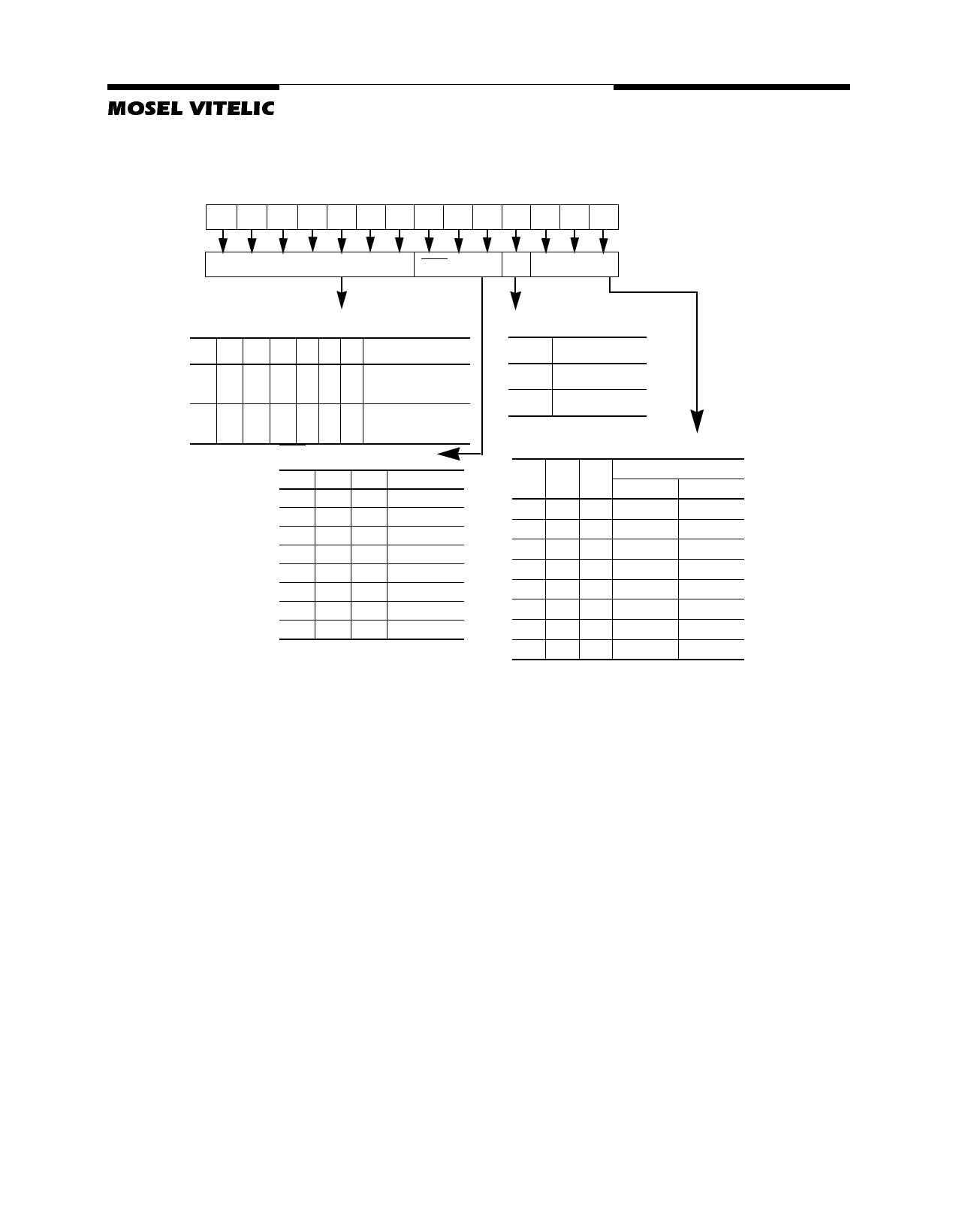

Address Input for Mode Set (Mode Register Operation)

V54C3128(16/80/40)4V(BGA)

BA1 BA0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Bus (Ax)

Operation Mode

CAS Latency BT Burst Length Mode Register

Operation Mode

BA1 BA0 A11 A10 A9 A8 A7

Mode

0

0

0

0 000

Burst Read/Burst

Write

0

0

0

0

100

Burst Read/Single

Write

CAS Latency

A6 A5 A4

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Latency

Reserve

Reserve

2

3

Reserve

Reserve

Reserve

Reserve

Similar to the page mode of conventional

DRAM’s, burst read or write accesses on any col-

umn address are possible once the RAS cycle

latches the sense amplifiers. The maximum tRAS or

the refresh interval time limits the number of random

column accesses. A new burst access can be done

even before the previous burst ends. The interrupt

operation at every clock cycles is supported. When

the previous burst is interrupted, the remaining ad-

dresses are overridden by the new address with the

full burst length. An interrupt which accompanies

Burst Type

A3

Type

0

Sequential

1

Interleave

Burst Length

Length

A2 A1 A0

Sequential Interleave

000

1

1

001

2

2

010

4

4

011

8

8

1 0 0 Reserve Reserve

1 0 1 Reserve Reserve

1 1 0 Reserve Reserve

1 1 1 Reserve Reserve

with an operation change from a read to a write is

possible by exploiting DQM to avoid bus contention.

When two or more banks are activated

sequentially, interleaved bank read or write

operations are possible. With the programmed

burst length, alternate access and precharge

operations on two or more banks can realize fast

serial data access modes among many different

pages. Once two or more banks are activated,

column to column interleave operation can be done

between different pages.

V54C3128(16/80/40)4V(BGA) Rev. 1.2 September 2001

9