MSM9405MB データシートの表示(PDF) - Oki Electric Industry

部品番号

コンポーネント説明

一致するリスト

MSM9405MB Datasheet PDF : 30 Pages

| |||

¡ Semiconductor

MSM9405

FUNCTIONAL DESCRIPTION

Modes

There are four modes provided by the MSM9405 for IrDA communication. Communication

with IrDA1.0 is in SIR mode or Extended-SIR mode, while communication with IrDA1.1 is in

MIR mode or FIR mode. In SIR mode, the MSM9405 has the necessary UART feature for IrDA

communication. The Extended-SIR mode is an original feature of the MSM9405. In this mode,

BOF/EOF insertion and CRC calculation/check are performed by the MSM9405. Therefore, the

burden to the CPU can be reduced compared with IrDA1.0 communication using ordinary

UART. Moreover, the Extended-SIR mode allows DMA transfer even in IrDA1.0 communication.

In MIR mode, IrDA1.1 communication at up to 1.152 Mbps is possible. The FIR mode supports

4 Mbps transfer for IrDA1.1. Features of each mode are as follows:

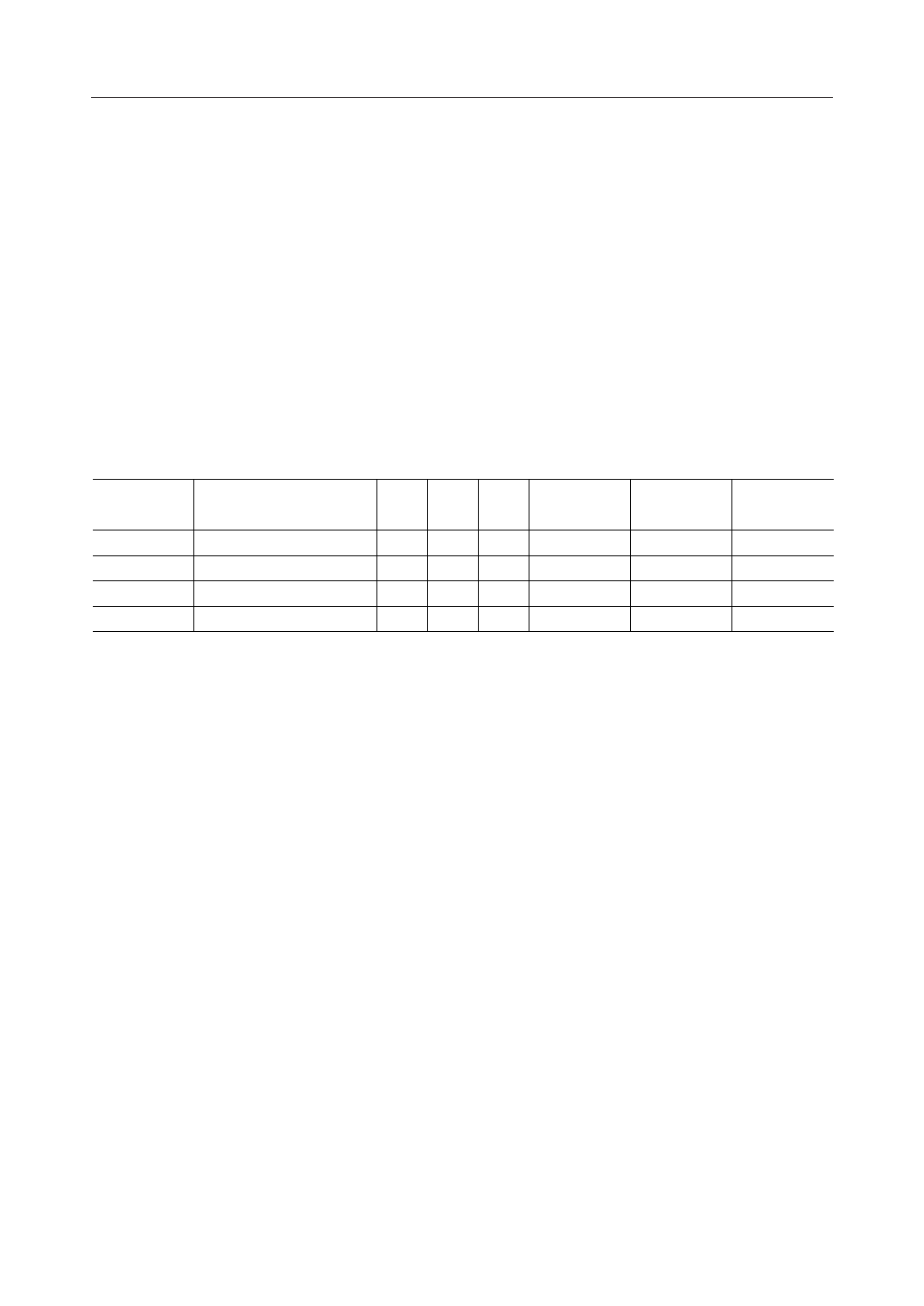

MSM9405 Modes Comparison

mode

SIR

Extended-SIR

MIR

FIR

Transfer rate

2.4 to 115.2 kbps

2.4 to 115.2 kbps

0.576, 1.152 Mbps

4 Mbps

BOF

SW

HW

HW

HW

Sending/Receiving Switching Method

CRC

SW

HW

HW

HW

EOF

SW

HW

HW

HW

CE insertion/ "0" insertion/ Preamble

removal

removal insertion/removal

SW

—

—

HW

—

—

—

HW

—

—

—

HW

CE : Control Escape Byte

SW : Software

HW : Hardware

Mode switching between sending and receiving is made using the TX_EN and RX_EN bits in

the ICR1 (Infrared Control Register 1). For sending, writing "1" in TX_EN puts the MSM9405

in the sending mode. Writing "1" in RX_EN puts the MSM9405 in the receiving mode. If "0" is

written to both TX_EN and RX_EN bits, the MSM9405 does not perform sending/receiving but

enters the idle state. Each register can be set even during the idle state. Data to be sent can be

written in advance to the FIFO during the idle state.

If "1" is written to both TX_EN and RX_EN, the MSM9405 is put in the receiving mode.

DMA Transfer

The MSM9405 allows DMA transfer. The DMA transfer mode covers the single transfer mode

and demand transfer mode, but not the block transfer mode. When a DMA controller with TC

output is used for sending, the DMA controller and MSM9405 automatically perform high-

speed transfer if the maximum frame length is specified for TFL and the transfer data length for

the TC counter of the DMA controller.

The timing when the DREQ signal is asserted is as follows:

During receiving, DREQ is asserted when data in the FIFO is at or above the receiving threshold

level or time-out occurs.

If all of the received data in the FIFO is read, DREQ is deasserted.

During sending, DREQ is asserted when data in the FIFO is lower than the sending threshold

level. Sent data is written and DREQ is deasserted when the FIFO becomes full or TXE_EV

occurs.

13/30