XRT83SH314 データシートの表示(PDF) - Exar Corporation

部品番号

コンポーネント説明

一致するリスト

XRT83SH314 Datasheet PDF : 101 Pages

| |||

XRT83SH314

14-CHANNEL T1/E1/J1 SHORT-HAUL LINE INTERFACE UNIT

PIN DESCRIPTIONS (BY FUNCTION)

REV. 1.0.4

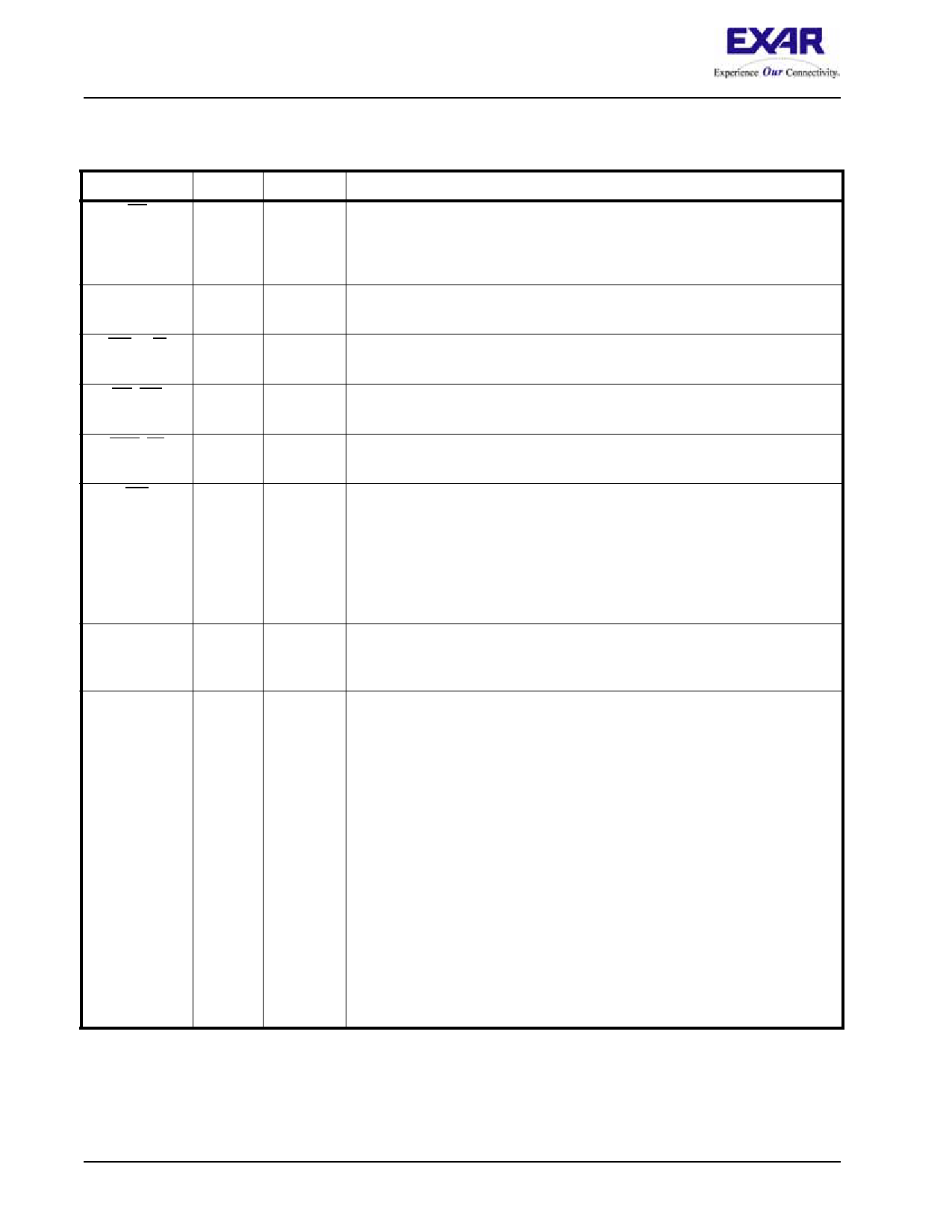

MICROPROCESSOR

NAME

PIN

TYPE

DESCRIPTION

CS

A22

I

Chip Select Input

Active low signal. This signal enables the microprocessor interface by pulling

chip select "Low". The microprocessor interface is disabled when the chip

select signal returns "High".

ALE_TS

C19

I

Address Latch Enable Input (Transfer Start)

See the Microprocessor section of this datasheet for a description.

WR_R/W

A20

I

Write Strobe Input (Read/Write)

See the Microprocessor section of this datasheet for a description.

RD_WE

D18

I

Read Strobe Input (Write Enable)

See the Microprocessor section of this datasheet for a description.

RDY_TA

AA3

O

Ready Output (Transfer Acknowledge)

See the Microprocessor section of this datasheet for a description.

INT

B3

O

Interrupt Output

Active low signal. This signal is asserted "Low" when a change in alarm status

occurs. Once the status registers have been read, the interrupt pin will return

"High". GIE (Global Interrupt Enable) must be set "High" in the appropriate

global register to enable interrupt generation.

NOTE: This pin is an open-drain output that requires an external 10KΩ pull-up

resistor.

µPCLK

AB2

I

Micro Processor Clock Input

In a synchronous microprocessor interface, µPCLK is used as the internal tim-

ing reference for programming the LIU.

ADDR10

ADDR9

ADDR8

ADDR7

ADDR6

ADDR5

ADDR4

ADDR3

ADDR2

ADDR1

ADDR0

A23

E20

C22

Y18

AA19

AB20

AC21

AB21

AA20

Y19

AC22

I

Address Bus Input

ADDR[10:8] is used as a chip select decoder. The LIU has 5 chip select output

pins for enabling up to 5 additional devices for accessing internal registers.

The LIU has the option to select itself (master device), up to 5 additional

devices, or all 6 devices simultaneously by setting the ADDR[10:8] pins speci-

fied below. ADDR[7:0] is a direct address bus for permitting access to the

internal registers.

ADDR[10:8]

000 = Master Device

001 = Chip Select Output 1 (Pin B21)

010 = Chip Select Output 2 (Pin D19)

011 = Chip Select Output 3 (Pin C20)

100 = Chip Select Output 4 (Pin A21)

101 = Chip Select Output 5 (Pin B20)

110 = Reserved

111 = All Chip Selects Active Including the Master Device

4