NJU3503L データシートの表示(PDF) - Japan Radio Corporation

部品番号

コンポーネント説明

一致するリスト

NJU3503L Datasheet PDF : 60 Pages

| |||

NJU3503

• PERIPHERAL REGISTERs(PH)

PERIPHERAL REGISTERs(PH) controlling I/O Ports or the ROM address are selected by the data in Y'-

reg.

Two Peripheral Register tables called as table0 and table1 in the NJU3503 consist of 32 registers totally.

The Peripheral Register assigned for each I/O Port can get the signal data from the external application

by reading operation, or can output the signal data to the external application by writing operation in

accordance with the type of input or output selected by the mask option. Although the data can be read

from the Peripheral Register assigned as the Output, it sometimes takes the incorrect data of the Output

Port.

<<Peripheral Register Table Change>>

When LSB(b0) of the peripheral register table change register(PHY0) is written “0”, the table0 is

selected. When LSB of PHY0 is written “1”, the table1 is selected.

The table0 is selected on “RESET” operation.

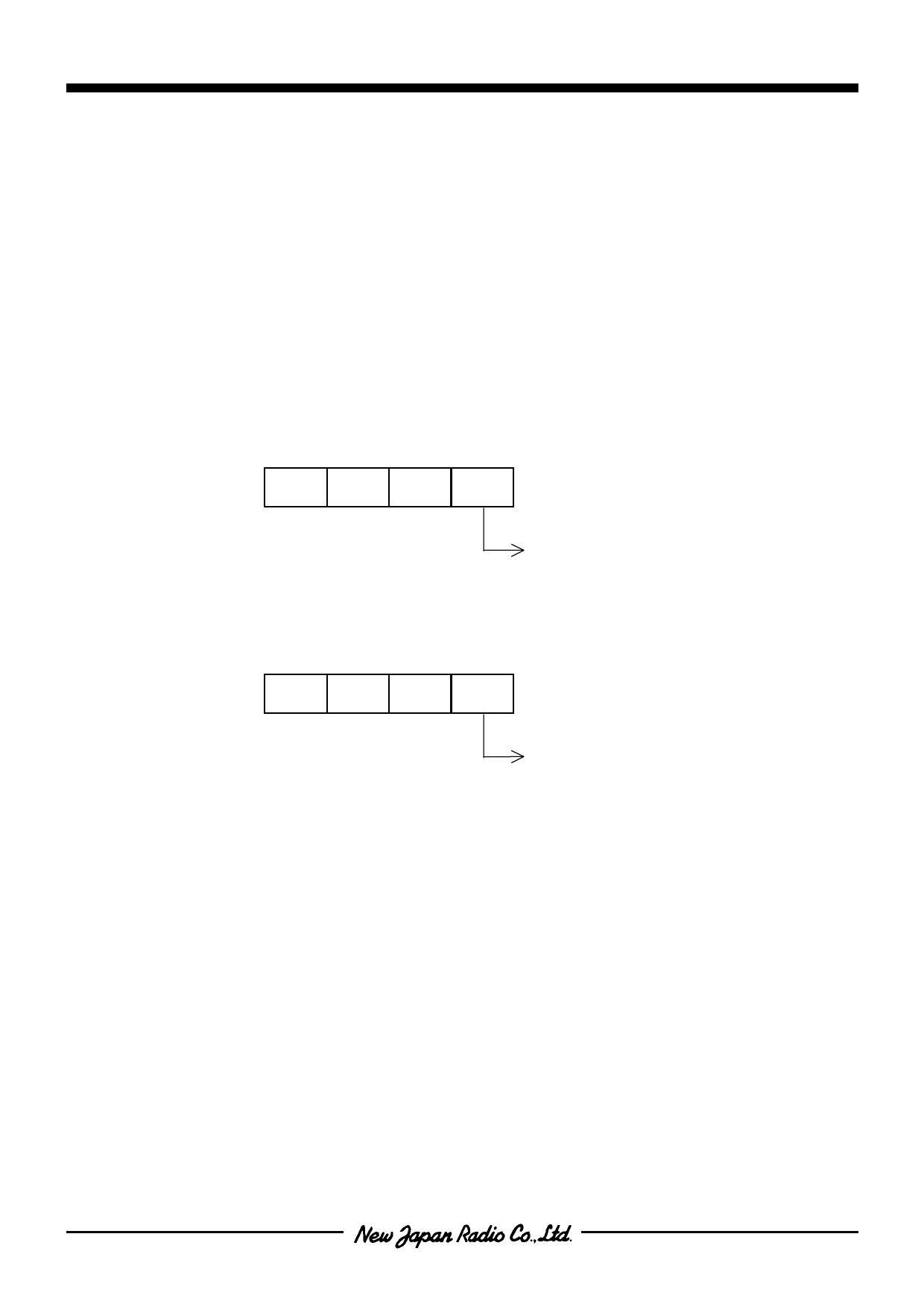

[ Reading from the Peripheral Register Table Change Register (PHY0) ]

(MSB) 3

2

1

PHY0

“0”

“0”

“0”

0 (LSB)

Peripheral register table

/ 0:table0, 1:table1

[ Writing to the Peripheral Register Table Change Register (PHY0) ]

(MSB) 3

2

1

PHY0

−

−

−

0 (LSB)

Peripheral register table set

/ 0:table0, 1:table1

- 11 -