MSM7718-01 データシートの表示(PDF) - Oki Electric Industry

部品番号

コンポーネント説明

一致するリスト

MSM7718-01 Datasheet PDF : 38 Pages

| |||

¡ Semiconductor

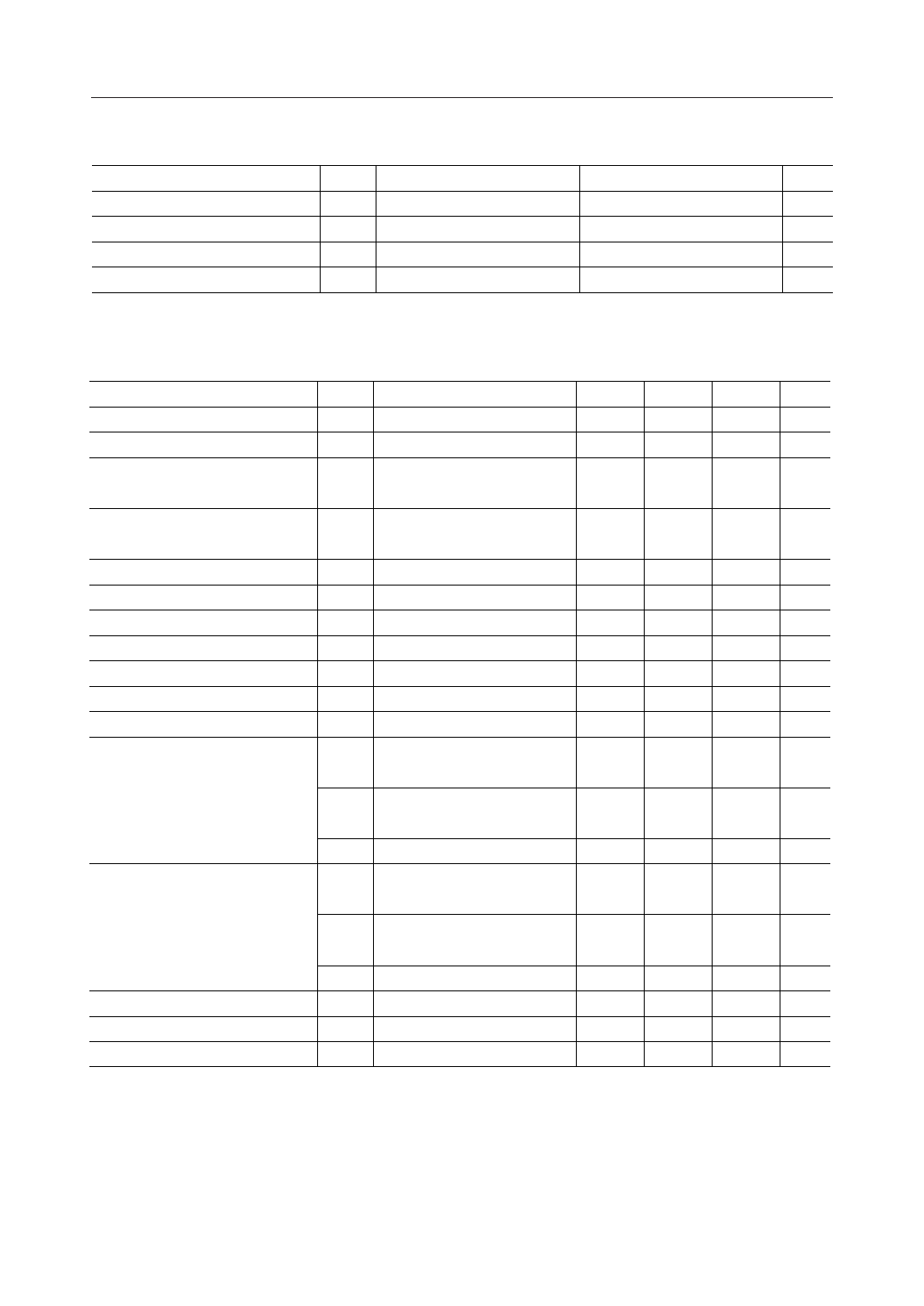

ABSOLUTE MAXIMUM RATINGS

Parameter

Power Supply Voltage

Analog Input Voltage

Digital Input Voltage

Storage Temperature

Symbol

VDD

VAIN

VDIN

TSTG

Condition

—

—

—

—

MSM7718-01

Rating

–0.3 to +5

– 0.3 to VDD + 0.3

–0.3 to VDD + 0.3

–55 to +150

Unit

V

V

V

°C

RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Condition

(VDD = 2.7 V to 3.6 V, Ta = –25°C to +70°C)

Min. Typ. Max. Unit

Power Supply Voltage

VDD

—

Operating Temperature

Ta

—

2.7

—

3.6

V

–25

+25

+70

°C

Input High Voltage

VIH All digital inputs

0.45

—

—

V

¥ VDD

Input Low Voltage

VIL All digital inputs

0.16

0

—

V

¥ VDD

Digital Input Rise Time

Digital Input Fall Time

tIr All digital inputs

tIf All digital inputs

—

—

50

ns

—

—

50

ns

Master Clock Frequency

fMCK MCK

–100ppm 19.2/9.6 +100ppm MHz

Master Clock Duty Ratio

DC MCK

40

50

60

%

Bit Clock Frequency

fBCK BCLKP, BCLKA

64

—

2048 kHz

Synchronous Pulse Frequency

fSYNC SYNCP, SYNCA

–1000ppm 8.0 +1000ppm kHz

Clock Duty Cycle

DCK BCLKP, BCLKA, EXCK

40

50

60

%

tXS

BCLKP to SYNCP,

BCLKA to SYNCA

100

—

—

ns

Transmit Sync Pulse Setting Time

SYNCP to BCLKP,

tSX SYNCA to BCLKA

100

—

—

ns

tXO SYNCP to BCLKP, SYNCA to BCLKA —

—

100

ns

BCLKP to SYNCP,

tRS BCLKA to SYNCA

100

—

—

ns

Receive Sync Pulse Setting Time

SYNCP to BCLKP,

tSR SYNCA to BCLKA

100

—

—

ns

tRO SYNCP to BCLKP, SYNCA to BCLKA —

—

Receive Sync Pulse Setting Time tWS SYNCP, SYNCA

1 BCLK —

PCM, ADPCM Setup Time

tDS

—

100

—

PCM, ADPCM Hold Time

tDH

—

100

—

100

ns

100

ms

—

ns

—

ns

Note: If SYNCP and SYNCA are generated from different clocks, do not change the relative

timing of the rising edge of SYNCP and that of SYNCA (that is, which rising edge is

earlier) after the reset state has been released.

14/38