MM74HC32 データシートの表示(PDF) - Fairchild Semiconductor

部品番号

コンポーネント説明

一致するリスト

MM74HC32 Datasheet PDF : 9 Pages

| |||

February 2008

MM74HC32

Quad 2-Input OR Gate

Features

■ Typical propagation delay: 10ns

■ Wide power supply range: 2V–6V

■ Low quiescent current: 20µA maximum (74HC Series)

■ Low input current: 1µA maximum

■ Fanout of 10 LS-TTL loads

General Description

The MM74HC32 OR gates utilize advanced silicon-gate

CMOS technology to achieve operating speeds similar to

LS-TTL gates with the low power consumption of stan-

dard CMOS integrated circuits. All gates have buffered

outputs providing high noise immunity and the ability to

drive 10 LS-TTL loads. The 74HC logic family is func-

tionally as well as pin-out compatible with the standard

74LS logic family. All inputs are protected from damage

due to static discharge by internal diode clamps to VCC

and ground.

Ordering Information

Package

Order Number Number

Package Description

MM74HC32M

MM74HC32SJ

MM74HC32MTC

M14A

M14D

MTC14

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

MM74HC32N

N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number.

All packages are lead free per JEDEC: J-STD-020B standard.

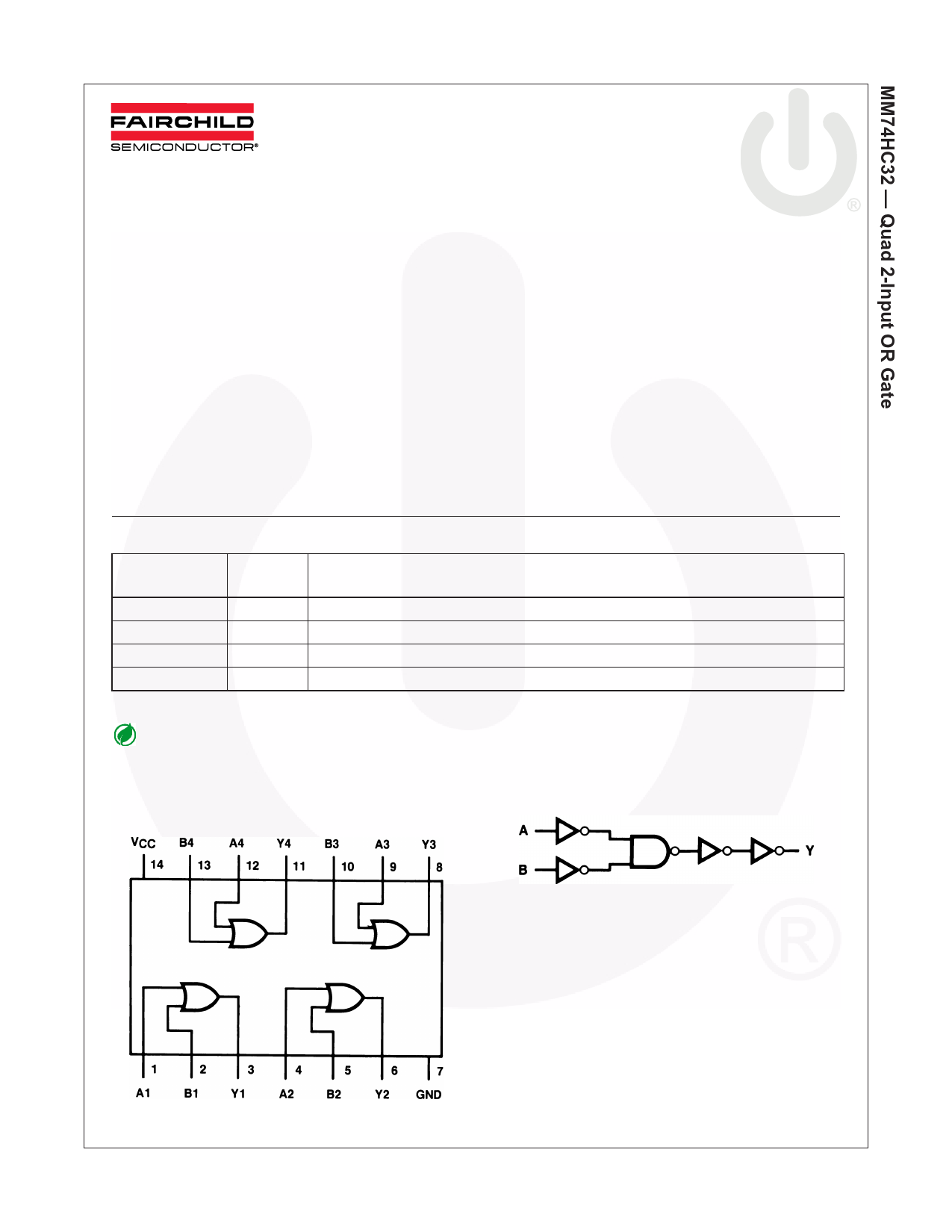

Connection Diagram

Pin Assignments for DIP, SOIC, SOP and TSSOP

Logic Diagram

Y=A+B

(1 of 4)

Top View

©1983 Fairchild Semiconductor Corporation

MM74HC32 Rev. 1.3.0

www.fairchildsemi.com