STPCE1 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

一致するリスト

STPCE1 Datasheet PDF : 87 Pages

| |||

GENERAL DESCRIPTION

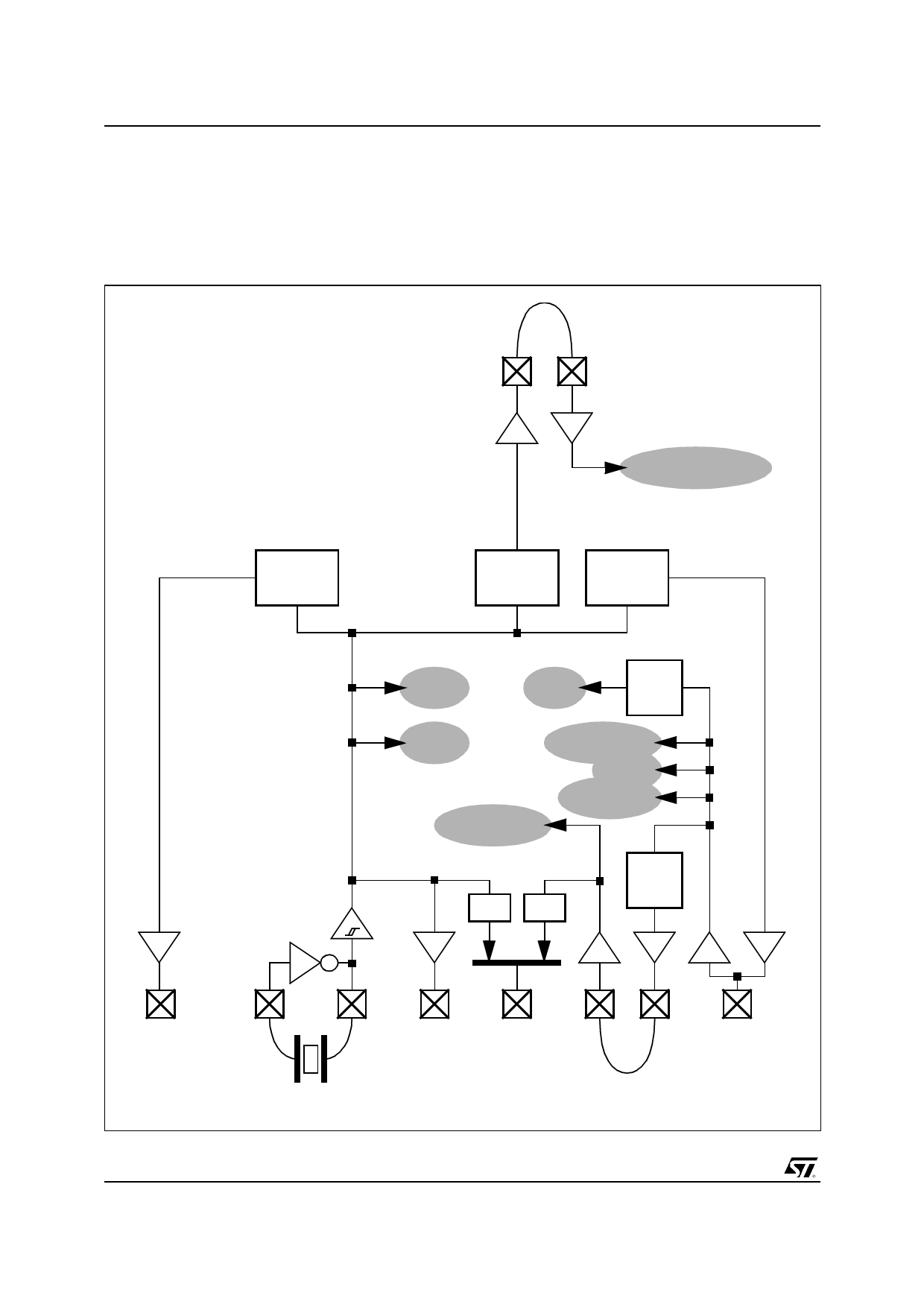

1.4. CLOCK TREE

The STPC Elite integrates many features and

generates all its clocks from a single 14MHz

oscillator. This results in multiple clock domains as

described in Figure 1-2.

The speed of the PLLs is either fixed (DEVCLK),

either programmable by strap option (HCLK)

either programmable by software (GPCLK,

MCLK). When in synchronized mode, MCLK

speed is fixed to HCLKO speed and HCLKI is

generated from MCLKI.

Figure 1-2. STPC Elite clock architecture

MCLKO

MCLKI

GPCLK

PLL

SDRAM controller

MCLK

PLL

HCLK HCLKO

PLL

ISA

CPU

x1 HCLKI

x2

IPC

South Bridge

North Bridge

Host

Local Bus

1/2

1/3

1/2 1/4

GPCLK

XTALO

XTALI

14.31818 MHz

OSC14M ISACLK

(14MHz)

PCICLKI

HCLK

PCICLKO

8/87

Release 1.3 - January 29, 2002

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.