ISP1562 データシートの表示(PDF) - NXP Semiconductors.

部品番号

コンポーネント説明

一致するリスト

ISP1562 Datasheet PDF : 94 Pages

| |||

NXP Semiconductors

ISP1562

HS USB PCI host controller

ISP1562_3

Product data sheet

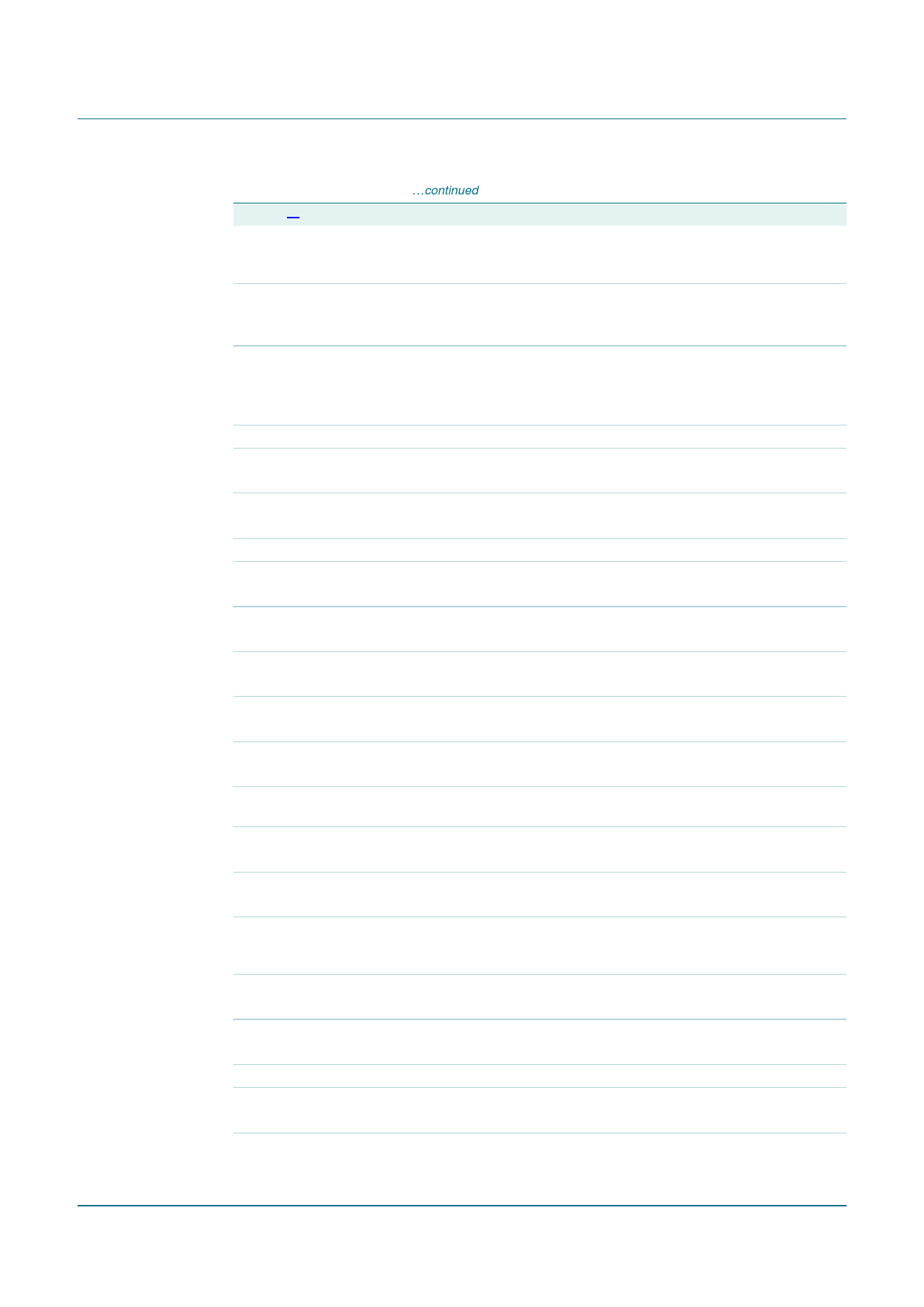

Table 2. Pin description …continued

Symbol[1] Pin Type Description

REG1V8 43 -

1.8 V regulator output voltage; only for voltage conditioning; cannot

be used to supply power to external components; add a 100 nF

decoupling capacitor

PERR#

44 I/O PCI parity error; used to report data parity errors during all PCI

transactions, except a special cycle

PCI pad; 3.3 V signaling

SERR#

45 O

PCI system error; used to report address parity errors and data parity

errors on the Special Cycle command, or any other system error in

which the result will be catastrophic

PCI pad; 3.3 V signaling; open-drain

GNDA

46 -

analog ground

PAR

47 I/O PCI parity

PCI pad; 3.3 V signaling

C/BE#[1] 48 I/O byte 1 of multiplexed PCI bus command and byte enable

PCI pad; 3.3 V signaling

GNDD

49 -

digital ground

AD[15]

50 I/O bit 15 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

AD[14]

51 I/O bit 14 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

AD[13]

52 I/O bit 13 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

AD[12]

53 I/O bit 12 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

AD[11]

54 I/O bit 11 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

VCC(I/O)

55 -

3.3 V supply voltage; used to power pads; add a 100 nF decoupling

capacitor

AD[10]

56 I/O bit 10 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

AD[9]

57 I/O bit 9 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

REG1V8 58 -

1.8 V regulator output voltage; only for voltage conditioning; cannot

be used to supply power to external components; add a 100 nF

decoupling capacitor

AD[8]

59 I/O bit 8 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

C/BE#[0] 60 I/O byte 0 of multiplexed PCI bus command and byte enable

PCI pad; 3.3 V signaling

GNDA

61 -

analog ground

AD[7]

62 I/O bit 7 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

AD[6]

63 I/O bit 6 of multiplexed PCI address and data

PCI pad; 3.3 V signaling

Rev. 03 — 14 November 2008

© NXP B.V. 2008. All rights reserved.

7 of 93