MWCT1001AVLH データシートの表示(PDF) - Freescale Semiconductor

部品番号

コンポーネント説明

一致するリスト

MWCT1001AVLH Datasheet PDF : 41 Pages

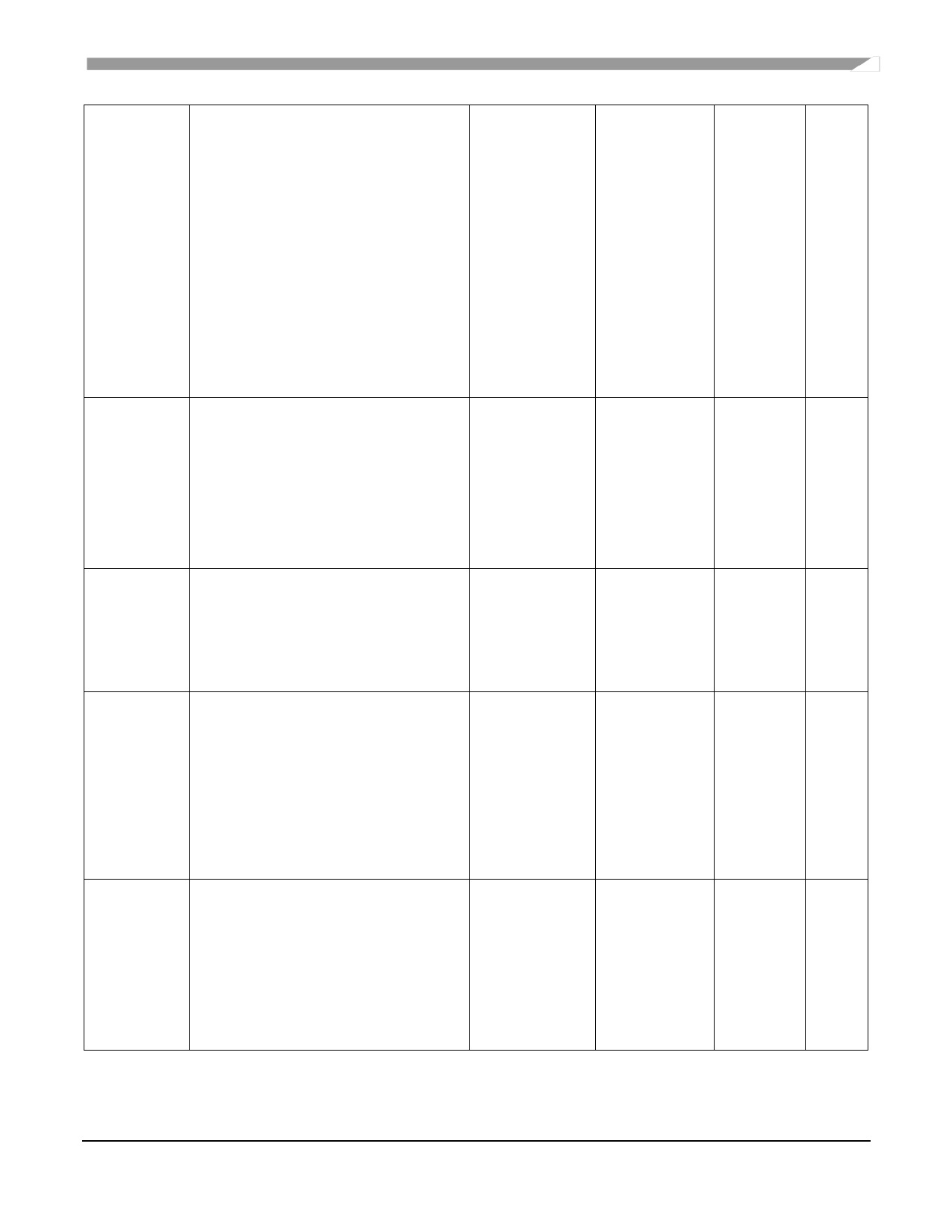

| |||

50 MHz/100 MHz5 core and peripheral

clock, regulators are in full regulation,

relaxation oscillator on, PLL powered on,

continuous MAC instructions with fetches

from program Flash, all peripheral modules

RUN2

enabled, TMRs and SCIs using 1×

peripheral clock, NanoEdge within

eFlexPWM using 2× peripheral clock,

9.07

50 MHz/100

25.62 mA/63.7

MHz5

mA/16.7

5

mA

mA

ADC/DAC (only one 12-bit DAC and all

6-bit DACs) powered on and clocked,

comparator powered on, all ports

configured as inputs with input low and no

DC loads

50 MHz/100 MHz5 core and peripheral

clock, regulators are in full regulation,

relaxation oscillator on, PLL powered on,

WAIT

core in WAIT state, all peripheral modules

enabled, TMRs and SCIs using 1× clock,

NanoEdge within eFlexPWM using 2×

clock, ADC/DAC (one 12-bit DAC, all 6-bit

50 MHz/100

MHz5

22.0 mA/43.5

mA

7.93

mA/13.58

µA

5

DACs)/comparator powered off, all ports

configured as inputs with input low and no

DC loads

STOP

4 MHz core and peripheral clock,

regulators are in full regulation, relaxation

oscillator on, PLL powered off, core in

STOP state, all peripheral module and

core clocks are off, ADC/DAC/Comparator

powered off, all ports configured as inputs

with input low and no DC loads

4 MHz

5.58 mA/9.19

1.77

uA/13.20

5

mA

uA

LPRUN

200 kHz core and peripheral clock from

relaxation oscillator's low speed clock,

relaxation oscillator in standby mode,

regulators are in standby, PLL disabled,

repeat NOP instructions, all peripheral

modules enabled, except NanoEdge within

eFlexPWM and cyclic ADCs, one 12-bit

DAC and all 6-bit DACs enabled, simple

loop with running from platform instruction

buffer, all ports configured as inputs with

input low and no DC loads

2 MHz

0.82

2.39 mA/1.86

mA/3.33

5

mA

mA

LPWAIT

200 kHz core and peripheral clock from

relaxation oscillator's low speed clock,

relaxation oscillator in standby mode,

regulators are in standby, PLL disabled, all

peripheral modules enabled, except

NanoEdge within eFlexPWM and cyclic

ADCs, one 12-bit DAC and all 6-bit DACs

enabled, core in WAIT mode, all ports

configured as inputs with input low and no

DC loads

2 MHz

0.81

2.37 mA/1.83

mA/2.67

5

mA

mA

Automotive Wireless Transmitter Controller, Rev. 1.0, 08/2014

Freescale Semiconductor

9