ICS9248F-103 データシートの表示(PDF) - Integrated Circuit Systems

部品番号

コンポーネント説明

一致するリスト

ICS9248F-103 Datasheet PDF : 16 Pages

| |||

ICS9248 - 103

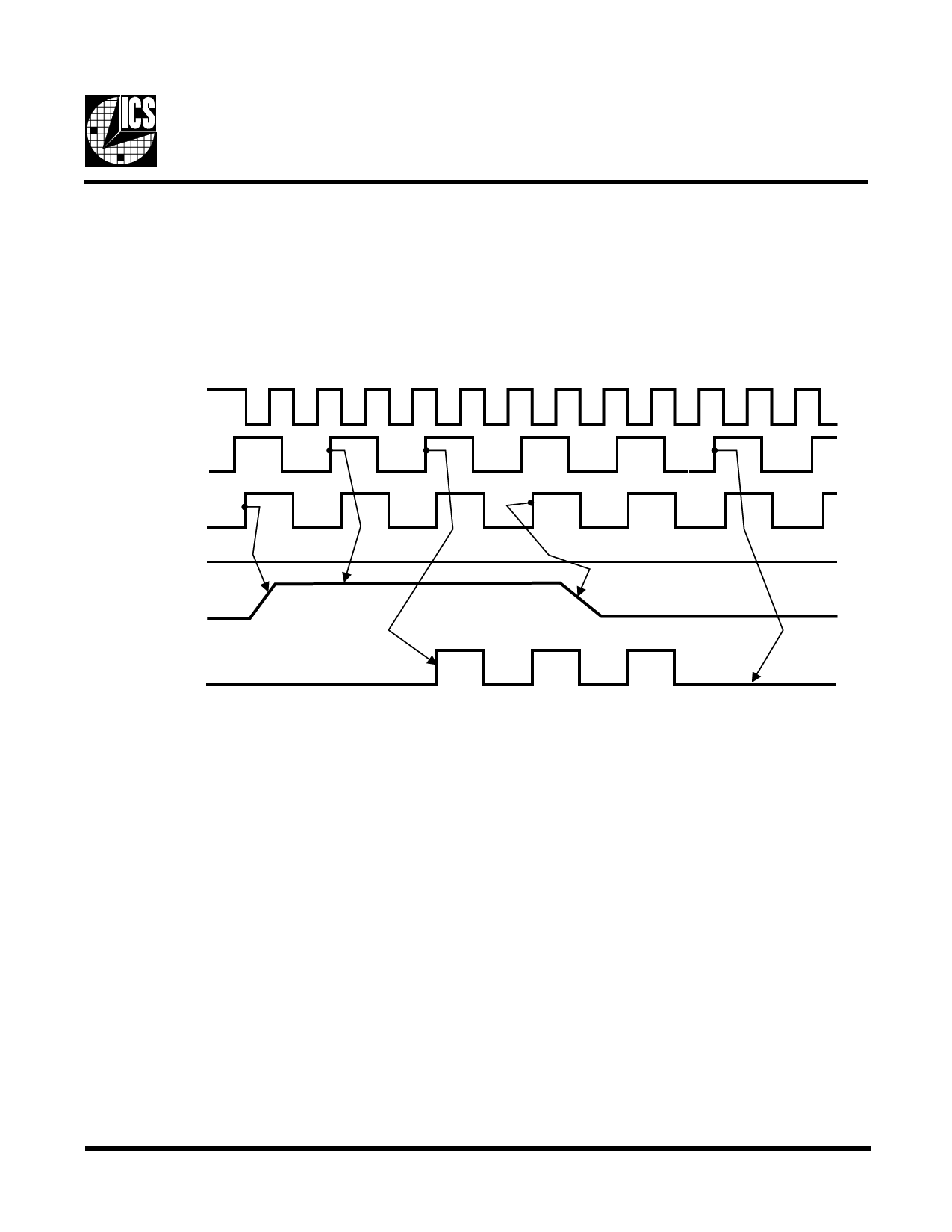

PCI_STOP# Timing Diagram

PCI_STOP# is an asynchronous input to the ICS9248-103. It is used to turn off the PCICLK [4:0] clocks for low power

operation. PCI_STOP# is synchronized by the ICS9248-103 internally. The minimum that the PCICLK [4:0] clocks are enabled

(PCI_STOP# high pulse) is at least 10 PCICLK [4:0] clocks. PCICLK [4:0] clocks are stopped in a low state and started with a full

high pulse width guaranteed. PCICLK [4:0] clock on latency cycles are only three rising PCICLK clocks off latency is one

PCICLK clock.

CPUCLK

(Internal)

PCICLK_F

(Internal)

PCICLK_F

(Free-running)

CLK_STOP#

PCI_STOP#

PCICLK [6:0]

Notes:

1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248 device.)

2. PCI_STOP# is an asynchronous input, and metastable conditions may exist. This signal is required to be synchronized

inside the ICS9248.

3. All other clocks continue to run undisturbed.

4. CLK_STOP# is shown in a high (true) state.

9