V827464K24S データシートの表示(PDF) - Mosel Vitelic Corporation

部品番号

コンポーネント説明

一致するリスト

V827464K24S

V827464K24S Datasheet PDF : 14 Pages

| |||

MOSEL VITELIC

V827464K24S

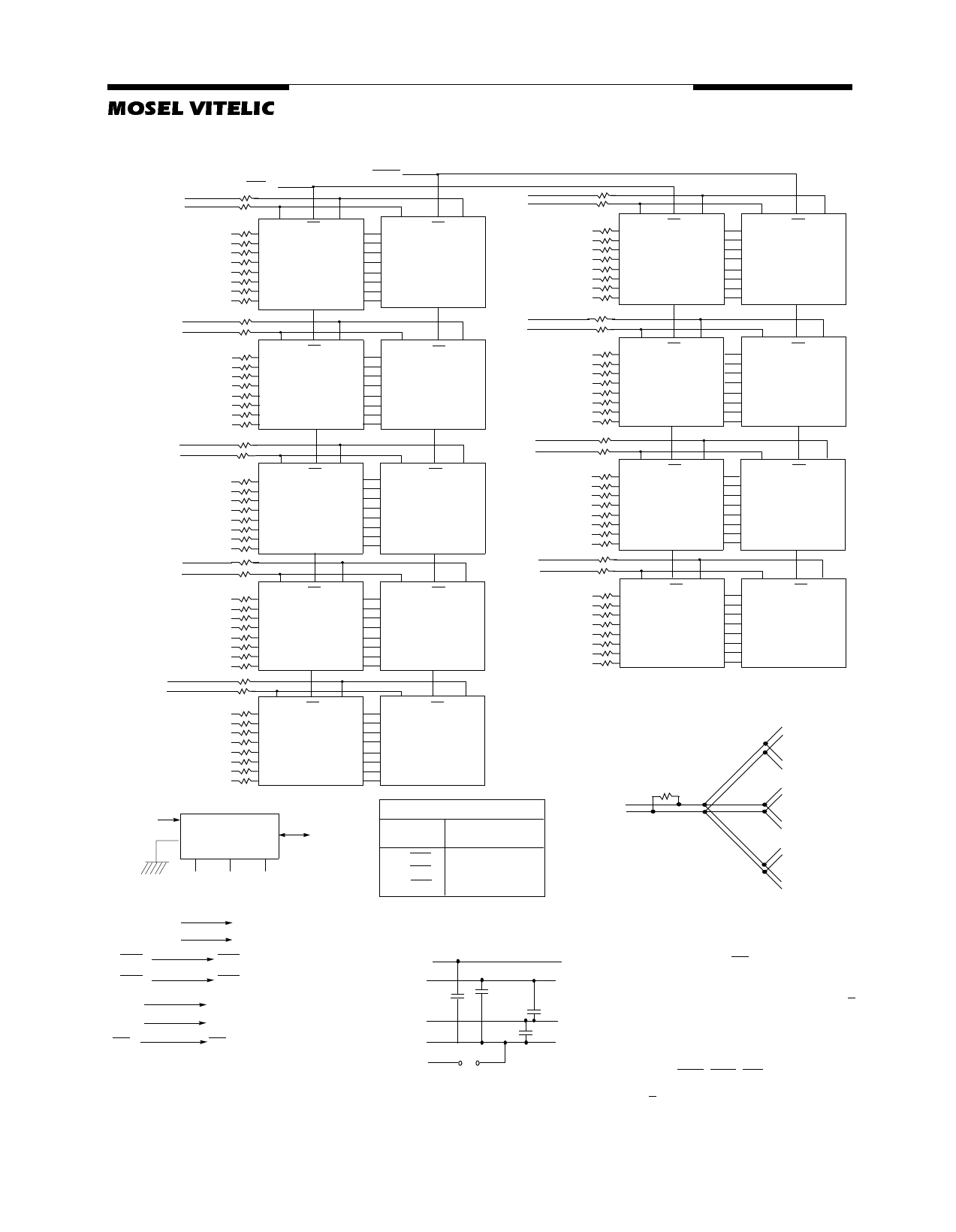

Block Diagram

DQS0

DM0

DQS1

DM1

DQS2

DM2

DQS3

DM3

DQS8

DM8

CS0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

Serial PD

SCL

WP

A0 A1 A2

SA0 SA1 SA2

CS DQS

D0

CS DQS

D1

CS DQS

D2

CS DQS

D3

CS DQS

D8

SDA

CS1

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DQS4

DM4

CS DQS

D9

DQS5

DM5

CS DQS

D10

CS DQS

DQS6

DM6

D11

CS DQS

D12

DQS7

DM7

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

CS DQS

D17

* Clock Wiring

Clock

Input

DDR SDRAMs

CK0/CK0

CK1/CK1

CK2/CK2

6 DDR SDRAMs

6 DDR SDRAMs

6 DDR SDRAMs

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

CS DQS

D4

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

CS DQS

D13

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

CS DQS

D5

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

CS DQS

D14

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

CS DQS

D6

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

CS DQS

D15

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DM

I/O 7

I/O 6

I/O 1

I/O 0

I/O 5

I/O 4

I/O 3

I/O 2

CS DQS

D7

DM

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

CS DQS

D16

*Clock Net Wiring

D3/D0/D5

R=120Ω

CK0/1/2

Card

Edge

*D8, D17 is assigned for ECC Comp.

D4/D1/D6

D8/D2/D7

D17/D9/D14

D12/D10/D15

D13/D11/D16

BA0 - BA1

A0 - A12

RAS

CAS

CKE1

CKE0

WE

BA0-BA1: DDR SDRAMs D0 - D17

A0-A12: DDR SDRAMs D0 - D17

RAS: DDR SDRAMs D0 - D17 VDDSPD

CAS: DDR SDRAMs D0 - D17 VDD/VDDQ

CKE: DDR SDRAMs D9 - D17

CKE: DDR SDRAMs D0 - D8

WE: DDR SDRAMs D0 - D17

VREF

VSS

VDDID

Notes:

1. DQ-to-I/O wiring is shown as recom-

mended but may be changed.

SPD 2. DQ/DQS/DM/CKE/CS relationships must

D0 - D17 be maintained as shown.

3. DQ, DQS, DM/DQS resistors: 22 Ohms +

D0 - D17 5%.

D0 - D17 4. VDDID strap connections

D0 - D17 (for memory device VDD, VDDQ):

STRAP OUT (OPEN): VDD = VDDQ

Strap: see Note 4 STRAP IN (VSS): VDD ≠ VDDQ.

5. BAx, Ax, RAS, CAS, WE resistors: 3

Ohms + 5%

V827464K24S Rev.1.1 September 2002

3