UPD72862 データシートの表示(PDF) - NEC => Renesas Technology

部品番号

コンポーネント説明

一致するリスト

UPD72862 Datasheet PDF : 36 Pages

| |||

µPD72862

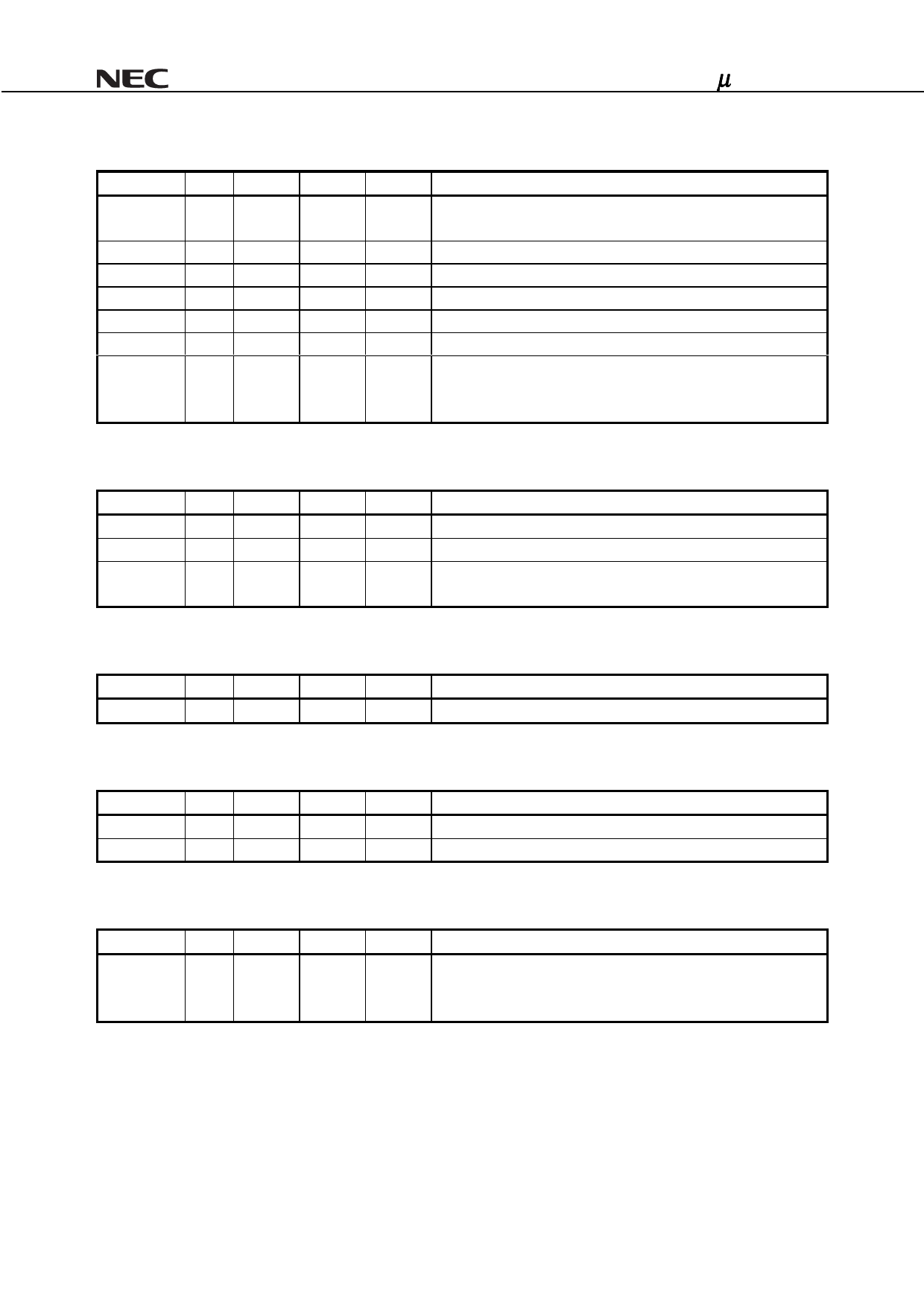

1.3 PHY/Link Interface Signals: (15 pins)

Name

D0-D7

CTL0,CTL1

LREQ

LINKON

LPS

SCLK

DIRECT

I/O Pin No.

I/O 59-62,

64-67

I/O 69, 70

O 73

I 77

O 74

I 72

I 68

IOL

9mA

9mA

9mA

-

9mA

-

-

Volts(V)

Function

3.3

PHY/Link Bi-directional Data (ISO-barrier supported)

3.3

PHY/Link Bi-directional Control (ISO-barrier supported)

3.3

PHY/Link Request (ISO-barrier supported)

3.3

Link-On Request (ISO-barrier supported)

3.3

Link Power Status (ISO-barrier supported)

3.3

PHY Clock 49.152 MHz (ISO-barrier supported)

3.3

Auxiliary PHY/Link Signal is used to determine whether the

interconnection between Link and PHY has isolation (‘low’: ISO-

barrier; ‘high’: no ISO-barrier).

1.4 Serial ROM Interface Signals: (3 pins)

Name

I/O Pin No.

GROM_SDA I/O 55

GROM_SCL O 56

GROM_EN

I 57

IOL

6mA

6mA

-

Volts(V)

3.3

3.3

3.3

Function

Serial EEPROM Data Input / Output

Serial EEPROM Clock Output

Serial EEPROM Enable (‘high’: GUID Load enabled; ‘low’: GUID

Load disabled)

1.5 Miscellaneous Signal: (1 pin)

Name

PIN_EN

I/O Pin No.

IOL

Volts(V)

Function

I 43

-

5/3.3 Pin Enable Input (High clamped)

1.6 IC: (3 pins)

Name

IC(H)

IC(L)

I/O Pin No.

IOL

Volts(V)

Function

I 44

-

3.3

Internally Connected (High clamped)

I 46, 47

-

3.3

Internally Connected (Low clamped)

1.7 NC: (5 pins)

Name

NC

I/O Pin No.

IOL

Volts(V)

Function

- 48, 49,

-

-

Non- Connection (Open)

52, 53,

Leave them unconnected.

58

1.8 VDD: (8 pins)

VDD (5 V PCI or 3.3 V PCI) for PCI I/Os: 11, 37, 92

VDD 3 V for digital core & PHY/Link I/Os: 1, 25, 51, 75, 97

1.9 VSS: (11 pins)

VSS : 6, 19, 26, 31, 38, 50, 63, 71, 76, 85, 100

10

Data Sheet S14265EJ2V0DS00