RTL8181 データシートの表示(PDF) - Realtek Semiconductor

部品番号

コンポーネント説明

一致するリスト

RTL8181 Datasheet PDF : 50 Pages

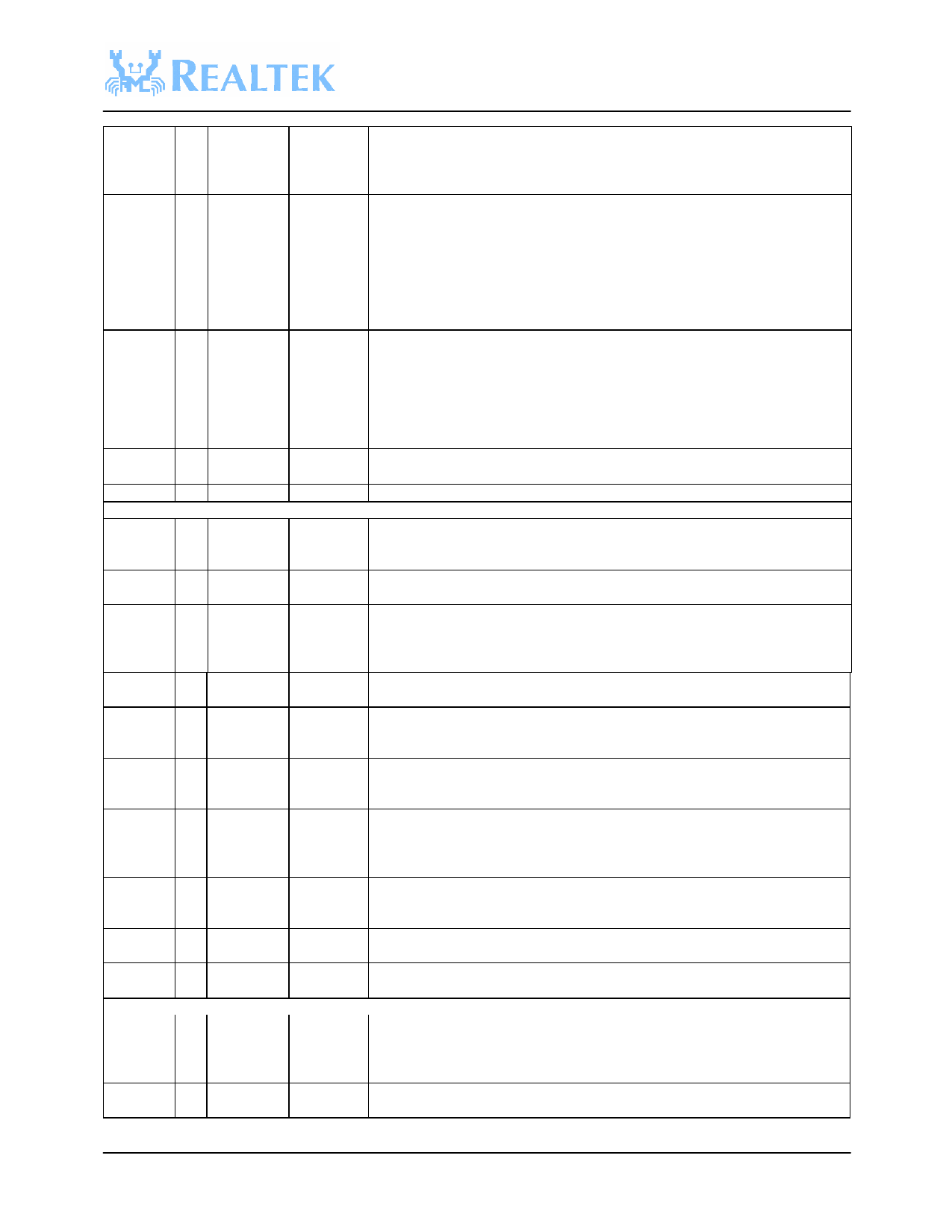

| |||

RTL8181

complete the current data phase transaction. This signal is used in conjunction

with the TRDYB signal. Data transaction takes place at the rising edge of CLK

when both IRDYB and TRDYB are asserted low. As a target, this signal indicates

that the master has put data on the bus.

TRDYB S/T/ *X

J19

Target Ready: This indicates the target agent’s ability to complete the current

S

phase of the transaction.

As a bus master, this signal indicates that the target is ready for the data during

write operations and with the data during read operations. As a target, this signal

will be asserted low when the (slave) device is ready to complete the current data

phase transaction. This signal is used in conjunction with the IRDYB signal. Data

transaction takes place at the rising edge of CLK when both IRDYB and TRDYB

are asserted low.

PAR

T/S *X

R2

Parity: This signal indicates even parity across AD31-0 and C/BE3-0 including

the PAR pin. PAR is stable and valid one clock after each address phase. For data

phase, PAR is stable and valid one clock after either IRDYB is asserted on a

write transaction or TRDYB is asserted on a read transaction. Once PAR is valid,

it remains valid until one clock after the completion of the current data phase. As

a bus master, PAR is asserted during address and write data phases. As a target,

PAR is asserted during read data phases.

STOPB S/T/ *X

B16

Stop: Indicates that the current target is requesting the master to stop the current

S

transaction.

RSTB O *X

B15

Reset: Active low signal to reset the PCI device.

MII Interface

LTXC, I 53,31

Y20

WTXC

W11

TXC is a continuous clock that provides a timing reference for the transfer of

TXD[3:0], TXE. In MII mode, it uses the 25 MHz or 2.5 MHz supplied by the

external PMD device.

LTXEN, O 59,37

T17

Indicates the presence of valid nibble data on TXD[3:0].

WTXEN

LTXD[3-0] O 57,56,55,54 V18,V17,W Four parallel transmit data lines which are driven synchronous t o the TXC for

, WTXD

35,34,33,32 19,W18 transmission by the external physical layer chip.

[3-0]

V12,Y13,W

12,Y12

LRXC, I 51,29

W17,V11 This is a continuous clock that is recovered from the incoming data. MRXC is

WRXC

25MHz in 100Mbps and 2.5Mhz in 10Mbs.

LCOL, I 60,38

U18,V13 This signal is asserted high synchronously by the external physical unit upon

WCOL

detection of a collision on the medium. It will remain asserted as long as the

collision condition persists.

LRXDV, I 43,44

W16,W9 Data valid is asserted by an external PHY when receive data is present on the

WRXDV

RXD[3:0] lines, and it is deasserted at the end of the packet. This signal is valid

on the rising of the RXC.

LRXD[3-0 I 50,49,47,46 V15,V16,Y This is a group of 4 data signals aligned on nibble boundaries which are driven

],

27,26,24,23 18,Y17,Y11 synchronous to the RXC by the external physical unit

WRXD[3-

,W10,V10,

0]

Y10

LRXER, I 44,22

V14,V9 This pin is asserted to indicate that invalid symbol has been detected in 100Mbps

WRXER

MII mode. This signal is synchronized to RXC and can be asserted for a

minimum of one receive clock.

LMDC, O 40,18

W15,W8 Management Data Clock: This pin provides a clock synchronous to MDIO,

WMDC

which may be asynchronous to the transmit TXC and receive RXC clocks.

LMDIO, I/O 41,19

Y16,Y9 Management Data Input/Output: This pin provides the bi-directional signal used

WMDIO

to transfer management information.

GPIO

GPIOB[11- I/O 205,206,207, U1,U2,U3, General purpose I/O pins group B pins 11 to 0. If ICFG[5-4] power on latch

0]

2,3,5,6,8,9,1 W1,Y1,Y2, =[1-0]. GPIO[5-2] mapping to JTAG_TDO(JTAG test data

1,12,13

W4,V5,Y4, output),JTAG_TRSTN(JTAG reset),JTAG_TMS(JTAG test mode

W5,V6,Y5 select),JTAG_TDI(JTAG test data input).

GPIOB[15 I/O 200,201,202, R1,T1,T2,T General purpose I/O pins group B pin 15 to 12.

-12]

203

3

CONFIDENTIAL

11

v1.0