MIC2590B データシートの表示(PDF) - Micrel

部品番号

コンポーネント説明

一致するリスト

MIC2590B Datasheet PDF : 23 Pages

| |||

Micrel, Inc.

Functional Description

Hot Swap Insertion

When circuit boards are inserted into systems carrying

live supply voltages (“hot plugged”), high inrush currents

often result due to the charging of bulk capacitance that

resides across the circuit board’s supply pins. This

transient inrush current can cause the system’s supply

voltages to temporarily go out of regulation, causing data

loss or system lock-up. In more extreme cases, the

transients occurring during a hot plug event may cause

permanent damage to connectors or on-board

components.

The MIC2590B addresses these issues by limiting the

inrush currents to the load (PCI Board), and thereby

controlling the rate at which the load’s circuits turn on. In

addition, the MIC2590B offers input and output voltage

supervisory functions and current-limiting to provide

robust protection for both the host system and the PCI

board.

System Interfaces

The MIC2590B employs two system interfaces. One is the

hot plug Interface (HPI) which includes ON[A/B],

AUXEN[A/B], and /FAULT[A/B]. The other is the System

Management Interface (SMI) consisting of SDA, SCL and

/INT, (whose signals conform to the specifications and

format of Intel’s SMBus standard). The MIC2590B can be

operated exclusively from the SMI, or can employ the HPI

for power control while continuing to use the SMI for

access to all but the power control registers.

In addition to the basic power control features of the

MIC2590B accessible by the HPI, the SMI also gives the

host access to the following information from the part:

1. Output voltage from each supply.

2. Output current from each supply.

3. Fault conditions occurring on each supply.

When using the System Management Interface for power

control, do not use the hot plug Interface. Conversely,

when using the HPI for power control, do not execute

power control commands over the SMI bus (all other

register accesses via the SMI bus remain permissible

while in the HPI control mode). Note that if power control

is performed via the SMIbus, the AUXENA, AUXENB,

ONA and ONB pins should be tied to ground.

Power-On Reset and Power Cycling

The MIC2590B utilizes VSTBY as the main supply input

source. It is required for proper operation of the

MIC2590B SMBus, registers and ADC and must be

applied at all times. A Power-On Reset (POR) cycle is

initiated after VSTBY rises above its UVLO threshold and

remains valid at that voltage for 500µs. All internal

registers except RESULT are cleared after POR. If VSTBY

is recycled the MIC2590B enters a new power-on reset

cycle. VSTBY must be the first supply input applied.

September 2008

MIC2590B

Following the POR interval, the MAIN supply inputs of

12VIN, 12MVIN, 5VIN and 3VIN may be applied in any order.

The SMBus is ready for access at the end of the POR

interval. During tPOR all outputs are off.

Power-Up Cycle (See Typical Application Circuit)

When a slot is off, the 5VGATE and 3VGATE pins are held

low with an internal pull-down current source. When a

slot’s main outputs are enabled, and all input voltages are

above their respective undervoltage lockout thresholds, all

four main supplies execute a controlled turn on. At this

time, the GATE voltages of the 5V and 3.3V MOSFETs

are ramped at a controlled rate from 0V to approximately

11.5V. This is sufficient to fully enhance the external

MOSFETs for lowest possible DC losses. The ramp rate

is controlled by 25µA (typ.) current sources from the

GATE pins charging each CGATE. The magnitude and slew

rate of the output current is proportional to the value of

CGATE and the load capacitance. The minimum value of

CGATE is selected to ensure that during start-up the load

current does not exceed the current-limit threshold. The

following equation is used to determine the value of CGATE

(min):

CGATE (min)

=

IGATE

ILIM

× CLOAD

Where CLOAD is the load capacitance connected to the

3.3V and 5V outputs and ILIM and IGATE are respectively

the current-limit and gate charge current specifications as

given in the Electrical Characteristics table. The output

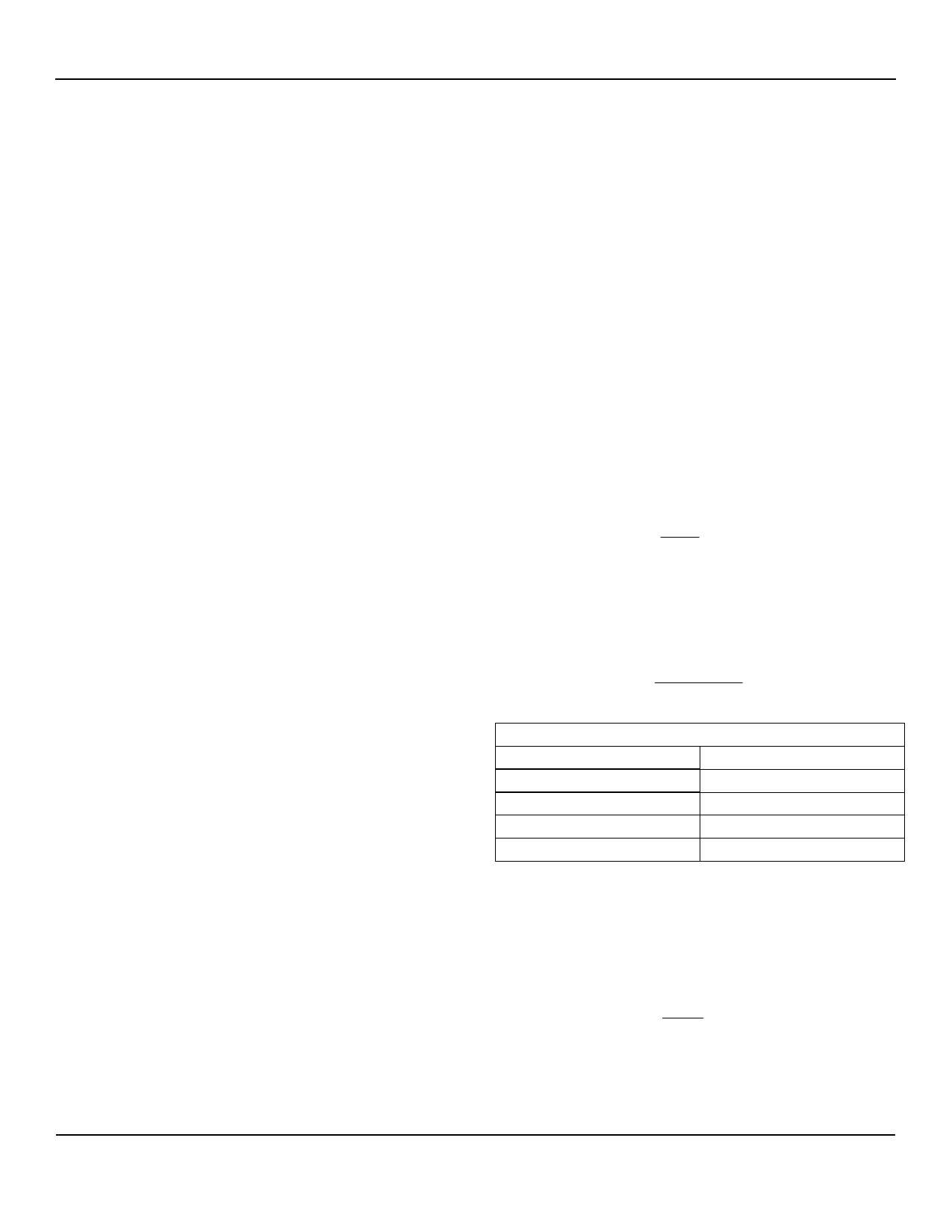

slew rate dv/dt is computed by:

dv/dt(load) = IGATE

CGATE × 10 6

CGATE

0.001µF

0.01µF

0.1µF

1µF

ISLEW = 25µA

dv/dt (load)

25000V/s

2500V/s

250V/s

25V/s

Table 1. 3.3V/5V Output Slew Rate Selection

For the +12V and –12V supplies, the output slew rate is

controlled by capacitors connected to the 12VSLEWA and

12VSLEWB pins. To determine the minimum value of the

slew rate capacitor, (CSLEW), connected to 12VSLEW[A/B],

the following equation is used:

C SLEW

(min)

=

ISLEW

ILIM

× CLOAD

where CLOAD is the load capacitance connected to the

+12V and –12V outputs, and ILIM and ISLEW are

respectively the current-limit and slew rate charge current

values found in the Electrical Characteristics table. The

11

M9999-091808