HSP3824 データシートの表示(PDF) - Harris Semiconductor

部品番号

コンポーネント説明

一致するリスト

HSP3824 Datasheet PDF : 41 Pages

| |||

HSP3824

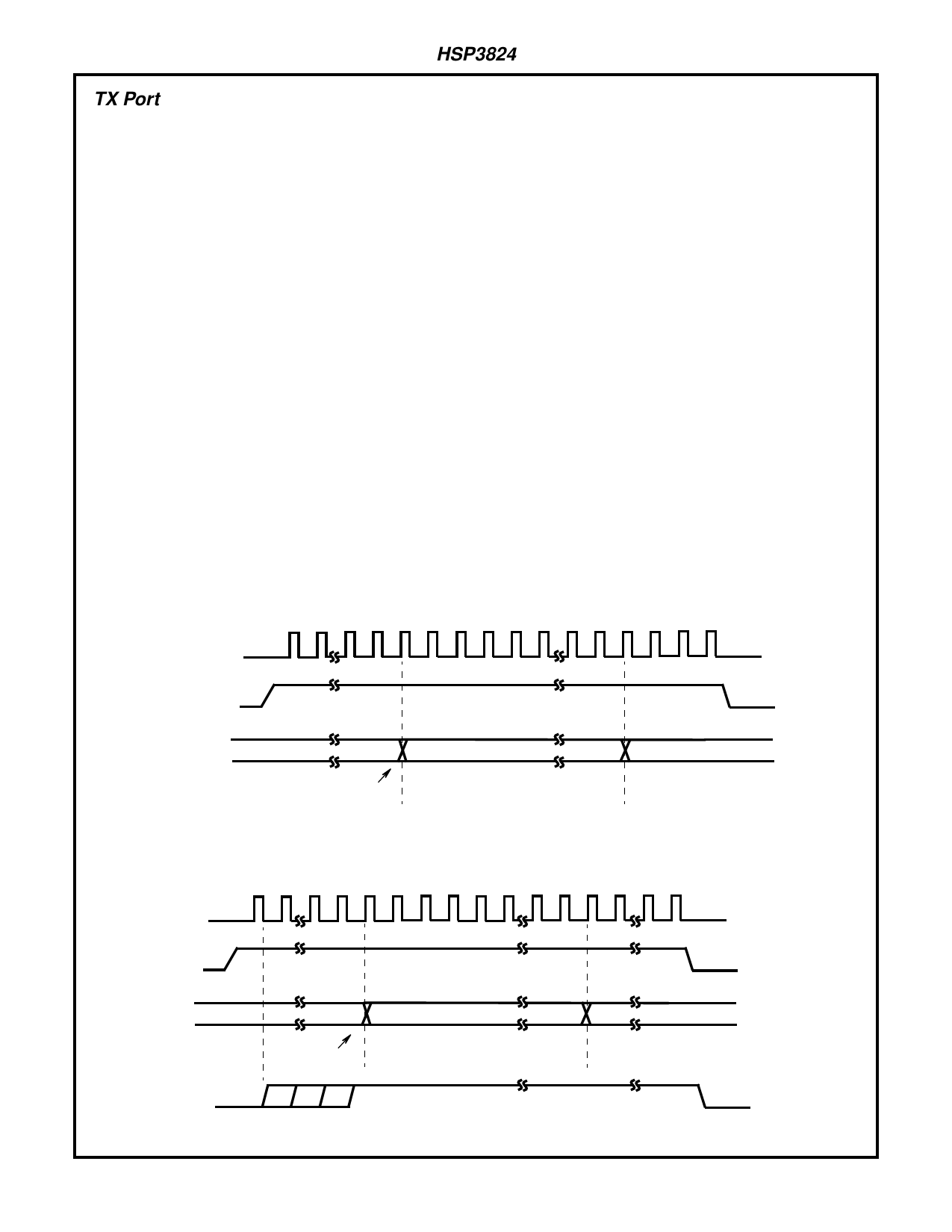

TX Port

The transmit data port accepts the data that needs to be

transmitted serially from an external data source. The data is

modulated and transmitted as soon as it is received from the

external data source. The serial data is input to the

HSP3824 through TXD using the falling edge of TXCLK to

clock it in the HSP3824. TXCLK is an output from the

HSP3824. A timing scenario of the transmit signal hand-

shakes and sequence is shown on timing diagram Figures 5

and 6.

The external processor initiates the transmit sequence by

asserting TX_PE. TX_PE envelopes the transmit data

packet on TXD. The HSP3824 responds by generating

TXCLK to input the serial data on TXD. TXCLK will run until

TX_PE goes back to its inactive state indicating the end of

the data packet. There are two possible transmit scenarios.

One scenario is when the HSP3824 internally generates the

preamble and header information. During this mode the

external source needs to provide only the data portion of the

packet. The timing diagram of this mode is illustrated on Fig-

ure 6. When the HSP3824 generates the preamble inter-

nally, assertion of TX_PE will initialize the generation of the

preamble and header. TX_RDY, which is an output from the

HSP3824, is used to indicate to the external processor that

the preamble has been generated and the device is ready to

receive the data packet to be transmitted from the external

processor. The TX_RDY timing is programmable in case the

external processor needs several clocks of advanced notice

before actual data transmission is to begin.

The second transmit scenario supported by the HSP3824 is

when the preamble and header information are provided by

the external data source. During this mode TX_RDY is not

required as part of the TX handshake. The HSP3824 will

immediately start transmitting the data available on TXD

upon assertion of TX_PE. The timing diagram of this TX sce-

nario, where the preamble and header are generated exter-

nal to the HSP3824, is illustrated on Figure 5.

One other signal that can be used for certain applications as

part of the TX interface is the Clear Channel Assessment

(CCA) signal which is an output from the HSP3824. The

CCA is programmable and it is described with more detail in

the Transmitter section of this document. CCA provides the

indication that the channel is clear of energy and the trans-

mission will not be subject to collisions. CCA can be moni-

tored by the external processor to assist in deciding when to

initiate transmissions. The CCA indication can bypassed or

ignored by the external processor. The state of the CCA

does not effect the transmit operation of the HSP3824.

TX_PE alone will always initiate the transmit state indepen-

dent of the state of CCA. Signals TX_RDY, TX_PE and

TXCLK can be set individually, by programming Configura-

tion Register (CR) 9, as either active high or active low sig-

nals.

The transmit port is completely independent from the opera-

tion of the other interface ports including the RX port, there-

fore supporting a full duplex mode.

TXCLK

TX_PE

TXD

PREAMBLE - HEADER LSB

DATA PACKET

MSB

DUMMY BITS TO CLEAR MOD PATH

MSB OF LAST HEADER FIELD

NOTE: Preamble/Header and Data is transmitted LSB first TX_RDY is inactive Logic 0 when generated externally. TXD shown generated

from rising edge TXCLK.

FIGURE 5. TX PORT TIMING (EXTERNAL PREAMBLE)

TXCLK

TX_PE

TXD

PREAMBLE - HEADER LSB

DATA PACKET

MSB DUMMY BITS TO CLEAR MOD PATH

MSB OF LAST HEADER FIELD

TX_RDY

NOTE: Preamble/Header and Data is transmitted LSB first. TXD shown generated from rising edge TXCLK. TX_RDY generated from falling edge.

FIGURE 6. TX PORT TIMING (INTERNAL PREAMBLE)

10