EL7562 データシートの表示(PDF) - Elantec -> Intersil

部品番号

コンポーネント説明

一致するリスト

EL7562 Datasheet PDF : 10 Pages

| |||

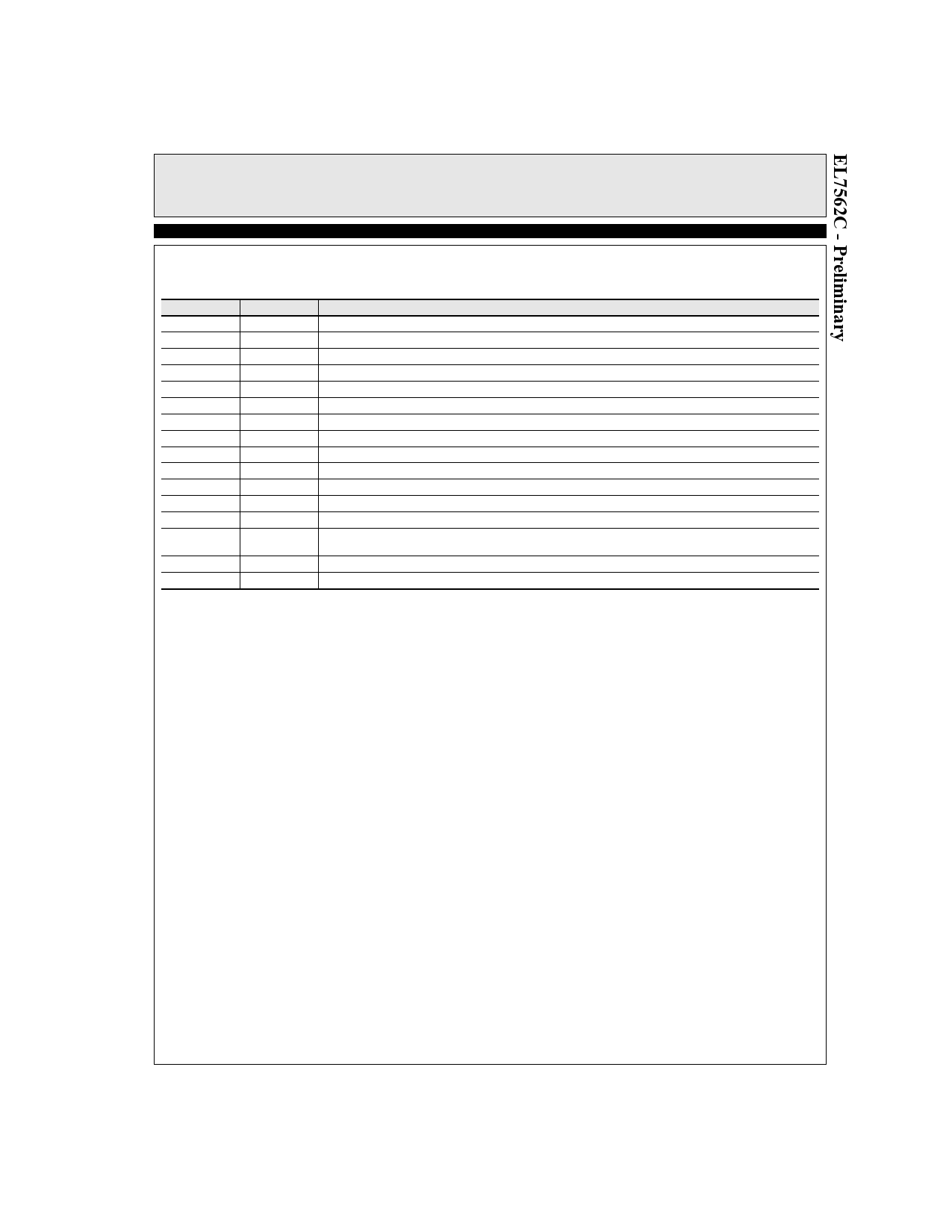

EL7562C - Preliminary

Monolithic 2 Amp DC:DC Step-down Regulator

Pin Descriptions

Pin Number

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Pin Name

SGND

COSC

VDD

PGND

PGND

VIN

VIN

EN

PGND

VHI

LX

LX

VDRV

FB

15

VREF

16

PGND

Pin Function

Control circuit negative supply.

Oscillator timing capacitor. FOSC can be approximated by: FOSC (kHz) = 0.1843/COSC, COSC in µF.

Control circuit positive supply.

Ground return of the regulator. Connected to the source of the low-side synchronous NMOS power FET.

Ground return of the regulator. Connected to the source of the low-side synchronous NMOS power FET.

Power supply input of the regulator. Connected to the drain of the high-side NMOS power FET.

Power supply input of the regulator. Connected to the drain of the high-side NMOS power FET.

Chip Enable, active high. A 2µA internal pull-up current enables the device if the pin is left open.

Ground return of the regulator.

Positive supply of the high-side driver.

Inductor drive pin. High current digital output whose average voltage equals the regulator output voltage.

Inductor drive pin. High current digital output whose average voltage equals the regulator output voltage.

Positive supply of the low-side driver and input voltage for the high-side boot strap.

Voltage feedback input. Connected to an external resistor divider between VOUT and GND. A 125nA pull-up current

forces VOUT to VS in the event that FB is floating.

Bandgap reference bypass capacitor. Typically 0.1µF to GND.

Ground return of the regulator.

3