PDI1394P11 データシートの表示(PDF) - Philips Electronics

部品番号

コンポーネント説明

一致するリスト

PDI1394P11 Datasheet PDF : 20 Pages

| |||

Philips Semiconductors

3-port physical layer interface

Product specification

PDI1394P11

1.0 FEATURES

• 3 cable interface ports

• Supports 100Mb/s and 200Mb/s transfers

• Interfaces to any 1394 standard Link Layer Controller

• 5V tolerant I/Os with Bus Holders

• Single 3.3V supply voltage

• Arbitrated (short) Bus Reset (1394a feature)

3.0 ORDERING INFORMATION

PACKAGE

TEMPERATURE RANGE

64-pin plastic LQFP

0°C to +70°C

2.0 DESCRIPTION

The Philips Semiconductors PDI1394P11 is an IEEE1394-1995

compliant Physical Layer interface. The PDI1394P11 provides the

analog physical layer functions needed to implement a three port

node in a cable-based IEEE 1394–1995 network. Additionally, the

device manages bus initialization and arbitration cycles, as well as

transmission and reception of data bits. The Link Layer Controller

interface is compatible with both 3V and 5V Link Controllers. While

providing a maximum transmission data rate of 200 Mb/s, the

PDI1394P11 is compatible with current 100 Mb/s Physical Layer

ICs. The PDI1394P11 is available in the LQFP64 package.

OUTSIDE NORTH AMERICA

PDI1394P11 BD

NORTH AMERICA

PDI1394P11 BD

PKG. DWG. #

SOT314-2

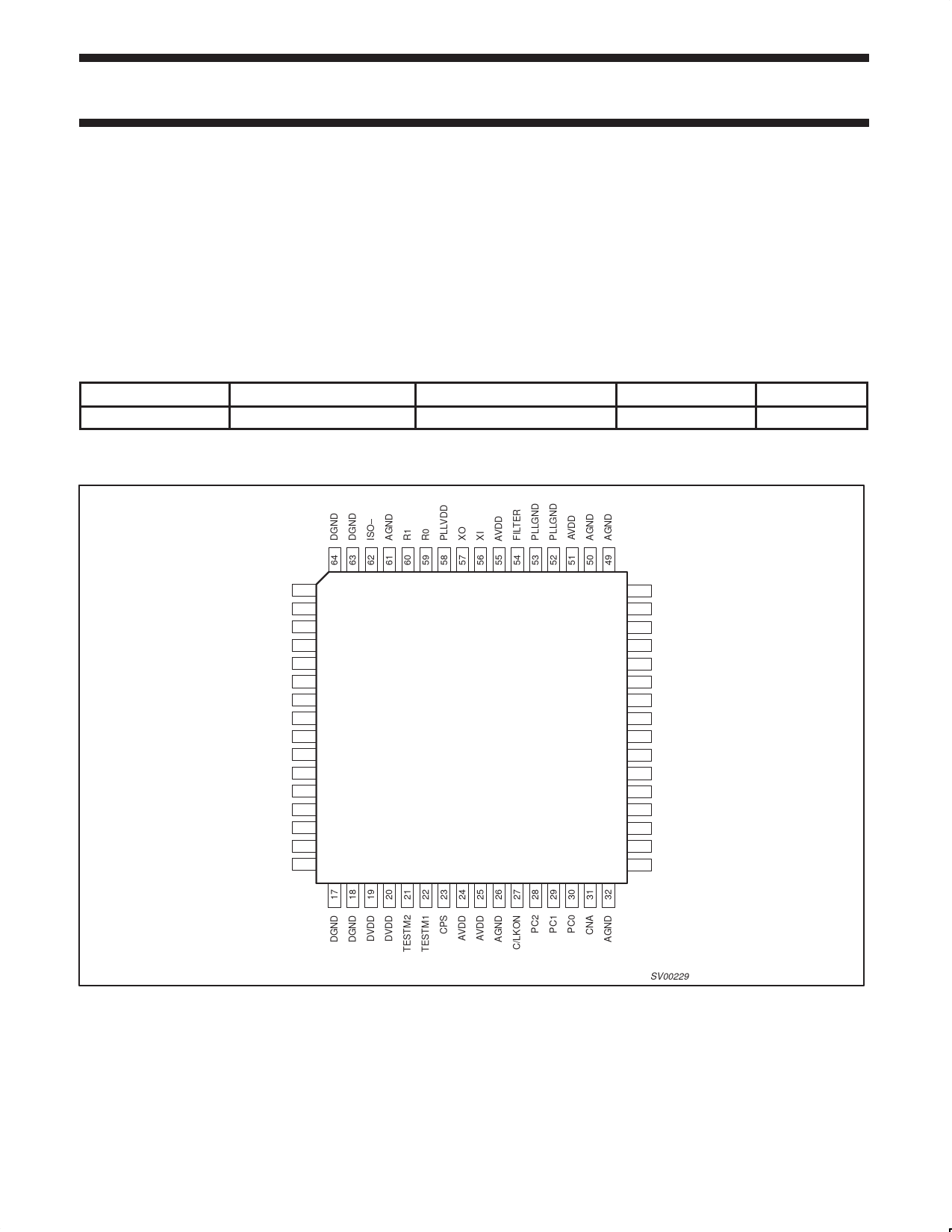

4.0 PIN CONFIGURATION

RESET– 1

LPS 2

LREQ 3

DVDD 4

DVDD 5

DVDD 6

PD 7

DGND 8

SYSCLK 9

DGND 10

CTL0 11

CTL1 12

D0 13

D1 14

D2 15

D3 16

PDI1394P11

48 TPBIAS3

47 TPBIAS2

46 TPBIAS1

45 TPA1+

44 TPA1–

43 TPB1+

42 TPB1–

41 AGND

40 TPA2+

39 TPA2–

38 TPB2+

37 TPB2–

36 TPA3+

35 TPA3–

34 TPB3+

33 TPB3–

SV00229

1999 Apr 09

2

853–2150 21222