A3908 データシートの表示(PDF) - Allegro MicroSystems

部品番号

コンポーネント説明

一致するリスト

A3908 Datasheet PDF : 8 Pages

| |||

A3908

Low Voltage DC Motor Driver

Functional Description

Voltage Regulation The A3908 regulates the voltage

across the motor coil. The voltage across the OUTA

and OUTB terminal is sensed and compared to an

internal threshold voltage. The high-side switch will

be driven in linear mode to keep the applied voltage

maintained at the calculated level, as follows:

VOUT = 4 × VREF (R2 / [R1+R2]) ,

where VREF (VBG) is 1.285 V typical.

Then, for forward mode:

VOUT = VOUTA – VOUTB ,

and for reverse mode:

VOUT = VOUTB – VOUTA .

The alternative method is to provide a tightly regu-

lated voltage to the motor supply pin and run the

source and sink drivers as switches. The voltage drop

across these switches will vary linearly with tempera-

ture and current, therefore the voltage across the motor

coil also will vary. The A3908 will eliminate these

sources of error for a system where controlling the

motor voltage is the optimum means of control.

Thermal Shutdown The A3908 will disable the out-

puts if the junction temperature, TJ , reaches 165°C.

There is 15°C of hysteresis, so when the junction

temperature drops below 150°C, the device will begin

to operate normally.

Dropout Mode The source and sink drivers have a

total RDS(on) of approximately 1.2 Ω total. When the

motor supply voltage, VDD, drops too low compared

to the regulated value, the IC enters dropout mode. In

this case, the voltage across the motor coil will be:

VMOTOR = VDD – ILOAD (RDS(sink) + RDS(src))

Brake Mode When both inputs are high, the A3908

goes into high-side brake mode (turns on both source

drivers). There is no protection during braking, so care

must be taken to ensure that the peak current does not

exceed the absolute maximum current, IOUT.

Standby Mode To minimize battery drain, standby

mode will turn off all of the circuitry and draw typi-

cally less than 100 nA from the VDD line. There will

be a very short delay, approximately 2 μs, before

enabling the output drivers after release of standby

mode.

Power Dissipation. Power can be approximated

based on the below three components:

PD(src) = ILOAD (VDD –VREG) ,

PD(sink) = ILOAD × RDS(sink) , and

Pbias = VDD × IDD.

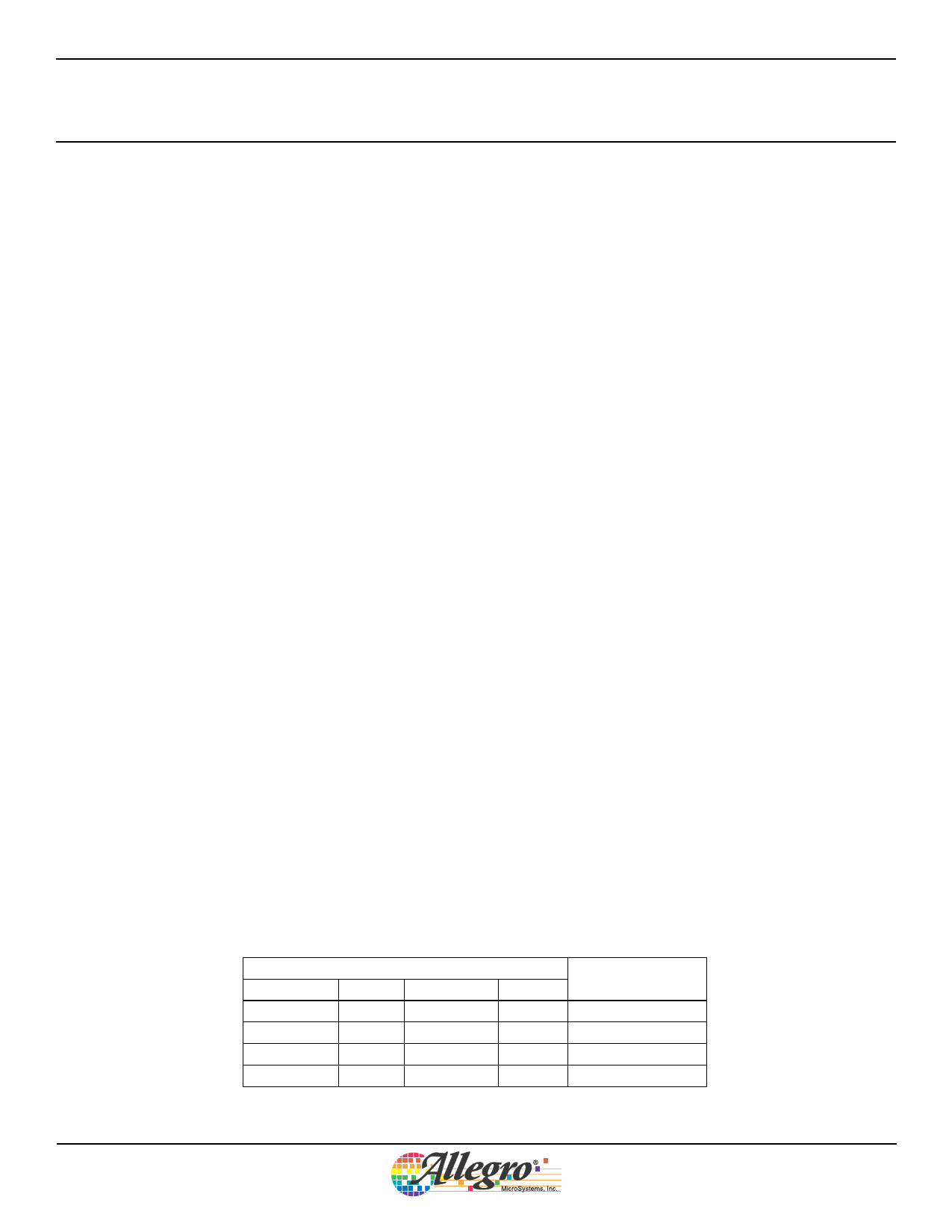

Control Logic Table

Settings

IN1

IN2

OUTA

0

0

Off

0

1

Low

1

0

VREG

1

1

High

OUTB

Off

VREG

Low

High

Resulting Mode

Standby

Reverse

Forward

Brake

Allegro MicroSystems, Inc.

5

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com