QL80FC データシートの表示(PDF) - QuickLogic Corporation

部品番号

コンポーネント説明

一致するリスト

QL80FC Datasheet PDF : 21 Pages

| |||

QL80FC - QuickFCTM

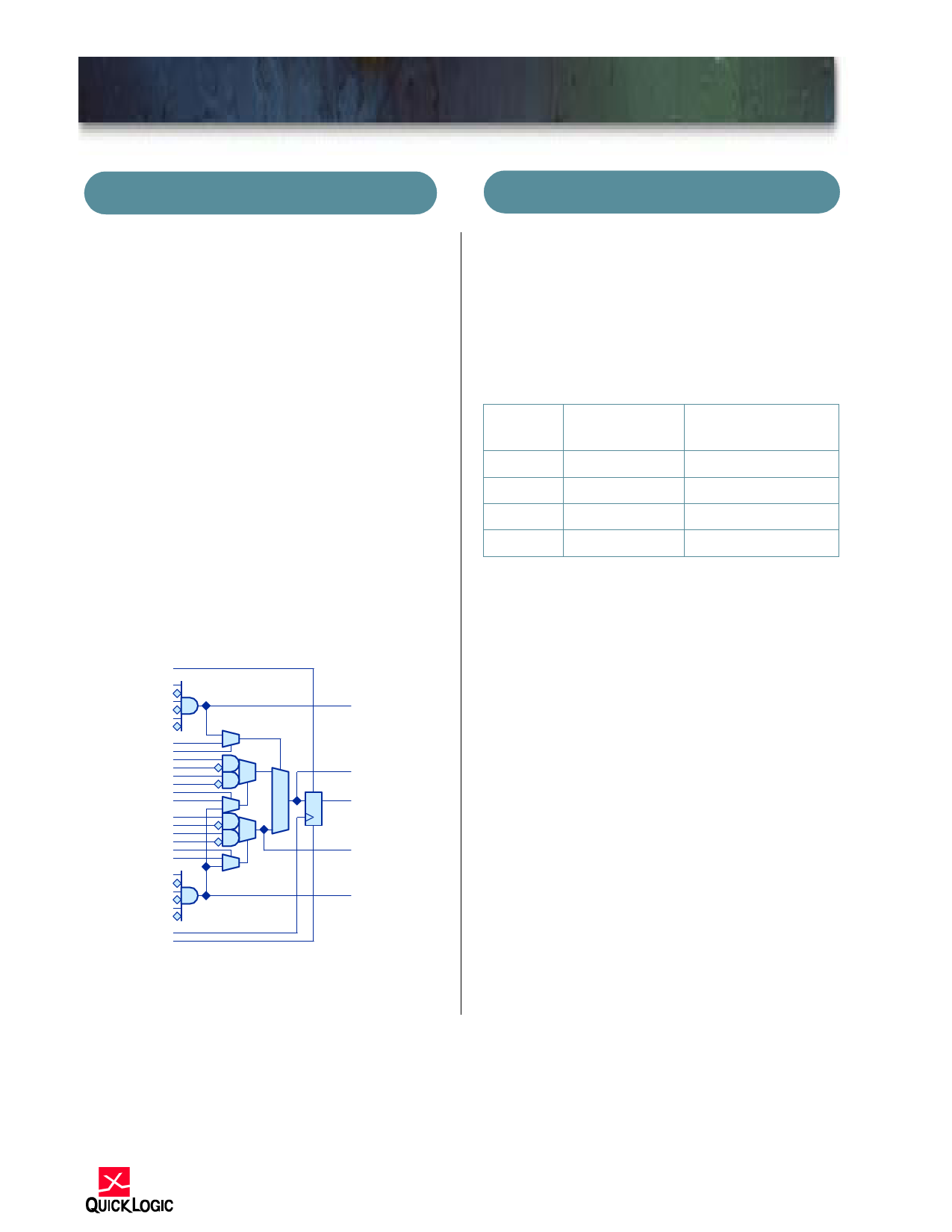

ARRAY OF LOGIC CELLS

A wide range of additional features complements the

QL80FC device. The FPGA portion of the device is

5-volt and 3.3-volt compliant and can perform high-

speed logic functions such as 160 MHz FIFOs. I/O

pins provide individually controlled output enables,

dedicated input/feedback registers, and full JTAG

capability for boundary scan and test. In addition, the

QL80FC device provides the benefits of non-volatil-

ity, high design security, immediate functionality on

power-up, and a single chip solution.

The QL80FC customizable logic architecture consists

of an array of user-configurable logic building blocks,

called logic cells, set beneath a grid of metal wiring

channels similar to those of a gate array. Through

ViaLink® elements located at the wire intersections,

the output(s) of any cell may be programmed to con-

nect to the input(s) of any other cell. Using the cus-

tomizable logic in the QL80FC, designers can quickly

and easily customize their “back-end” design for any

number of applications.

QS

A1

A2

A3

A4

AZ

A5

A6

OS

OP

B1

B2

C1

OZ

C2

MP

MS

QZ

D1

D2

E1

E2

NP

NZ

NS

F1

F2

F3

F4

FZ

F5

F6

QC

QR

FIGURE 4. Logic Cell

Array of Logic Cells

RAM MODULE FEATURES

The QL80FC device has 22 1,152-bit RAM mod-

ules, for a total of 25,344 RAM bits. Using two

“mode” pins, designers can configure each module

into 64 (deep) x18 (wide), 128x9, 256x4, or 512x2

blocks. See the table below. The blocks are also eas-

ily cascadable to increase their effective width or

depth.

RAM Module Features

Mode:

64x18

128x9

256x4

512x2

Address

Buses [a:0]

[5:0]

[6:0]

[7:0]

[8:0]

Data Buses

[w:0]

[17:0]

[8:0]

[3:0]

[1:0]

The RAM modules are “dual-ported”, with com-

pletely independent READ and WRITE ports and

separate READ and WRITE clocks. The READ ports

support asynchronous and synchronous operation,

while the WRITE ports support synchronous opera-

tion. Each port has 18 data lines and 9 address lines,

allowing word lengths of up to 18 bits and address

spaces of up to 512 words. Depending on the mode

selected, however, some higher order data or address

lines may not be used.

9