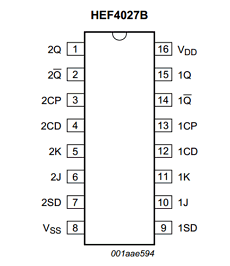

HEF4027BP データシート - NXP Semiconductors.

General description

The HEF4027B is a edge-triggered dual JK flip-flop which features independent set-direct (SD), clear-direct (CD), clock (CP) inputs and outputs (Q, Q). Data is accepted when CP is LOW, and transferred to the output on the positive-going edge of the clock. The active HIGH asynchronous clear-direct (CD) and set-direct (SD) inputs are independent and override the J, K, and CP inputs. The outputs are buffered for best system performance. Schmitt trigger action makes the clock input highly tolerant of slower rise and fall times.

It operates over a recommended VDD power supply range of 3 V to 15 V referenced to VSS (usually ground). Unused inputs must be connected to VDD, VSS, or another input.

FEATUREs and benefits

■ Fully static operation

■ 5 V, 10 V, and 15 V parametric ratings

■ Standardized symmetrical output characteristics

■ Specified from −40 °C to +85 °C

■ Complies with JEDEC standard JESD 13-B

APPLICATIONs

■ Registers

■ Counters

■ Control circuits