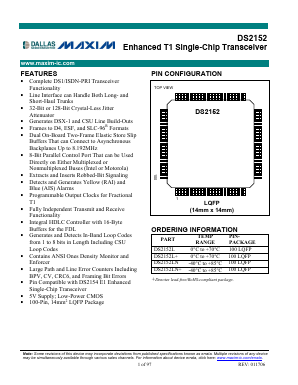

DS2152 データシート - Maxim Integrated

DETAILED DESCRIPTION

The DS2152 T1 enhanced single-chip transceiver (SCT) contains all the necessary functions for connection to T1 lines, whether they be DS-1 long haul or DSX-1 short haul. The clock recovery circuitry automatically adjusts to T1 lines from 0 feet to over 6000 feet in length. The device can generate both DSX-1 line build-outs as well as CSU line build-outs of -7.5dB, -15dB, and -22.5dB. The on-board jitter attenuator (selectable to either 32 bits or 128 bits) can be placed in either the transmit or receive data paths. The framer locates the frame and multiframe boundaries and monitors the data stream for alarms.

FEATURES

■ Complete DS1/ISDN-PRI Transceiver Functionality

■ Line Interface can Handle Both Long- and Short-Haul Trunks

■ 32-Bit or 128-Bit Crystal-Less Jitter Attenuator

■ Generates DSX-1 and CSU Line Build-Outs

■ Frames to D4, ESF, and SLC-96R Formats

■ Dual On-Board Two-Frame Elastic Store Slip Buffers That can Connect to Asynchronous Backplanes Up to 8.192MHz

■ 8-Bit Parallel Control Port That can be Used Directly on Either Multiplexed or Nonmultiplexed Buses (Intel or Motorola)

■ Extracts and Inserts Robbed-Bit Signaling

■ Detects and Generates Yellow (RAI) and Blue (AIS) Alarms

■ Programmable Output Clocks for Fractional T1

■ Fully Independent Transmit and Receive Functionality

■ Integral HDLC Controller with 16-Byte Buffers for the FDL

■ Generates and Detects In-Band Loop Codes from 1 to 8 bits in Length Including CSU Loop Codes

■ Contains ANSI Ones Density Monitor and Enforcer

■ Large Path and Line Error Counters Including BPV, CV, CRC6, and Framing Bit Errors

■ Pin Compatible with DS2154 E1 Enhanced Single-Chip Transceiver

■ 5V Supply; Low-Power CMOS

■ 100-Pin, 14mm2 LQFP Package

New Features

■ Option for non-multiplexed bus operation

■ Crystal-less jitter attenuation

■ Additional hardware signaling capability including:

– Receive signaling reinsertion to a backplane multiframe sync

– Availability of signaling in a separate PCM data stream

– Signaling freezing

– Interrupt generated on change of signaling data

■ Per-channel code insertion in both transmit and receive paths

■ Full HDLC controller for the FDL with 16-byte buffers in both transmit and receive paths

■ RCL, RLOS, RRA, and RAIS alarms now interrupt on change of state

■ 8.192MHz clock synthesizer

■ Per-channel loopback

■ Addition of hardware pins to indicate carrier loss and signaling freeze

■ Line interface function can be completely decoupled from the framer/formatter to allow:

– Interface to optical, HDSL, and other NRZ interfaces

– Ability to “tap” the transmit and receive bipolar data streams for monitoring purposes

– Ability to corrupt data and insert framing errors, CRC errors, etc.

■ Transmit and receive elastic stores now have independent backplane clocks

■ Ability to monitor one DS0 channel in both the transmit and receive paths

■ Access to the data streams in between the framer/formatter and the elastic stores

■ AIS generation in the line interface that is independent of loopbacks

■ Ability to calculate and check CRC6 according to the Japanese standard

■ Ability to pass the F-bit position through the elastic stores in the 2.048MHz backplane mode

■ Programmable in-band loop code generator and detector