ML7033 データシートの表示(PDF) - LAPIS Semiconductor Co., Ltd.

部品番号

コンポーネント説明

一致するリスト

ML7033 Datasheet PDF : 52 Pages

| |||

FEDL7033-04

ML7033

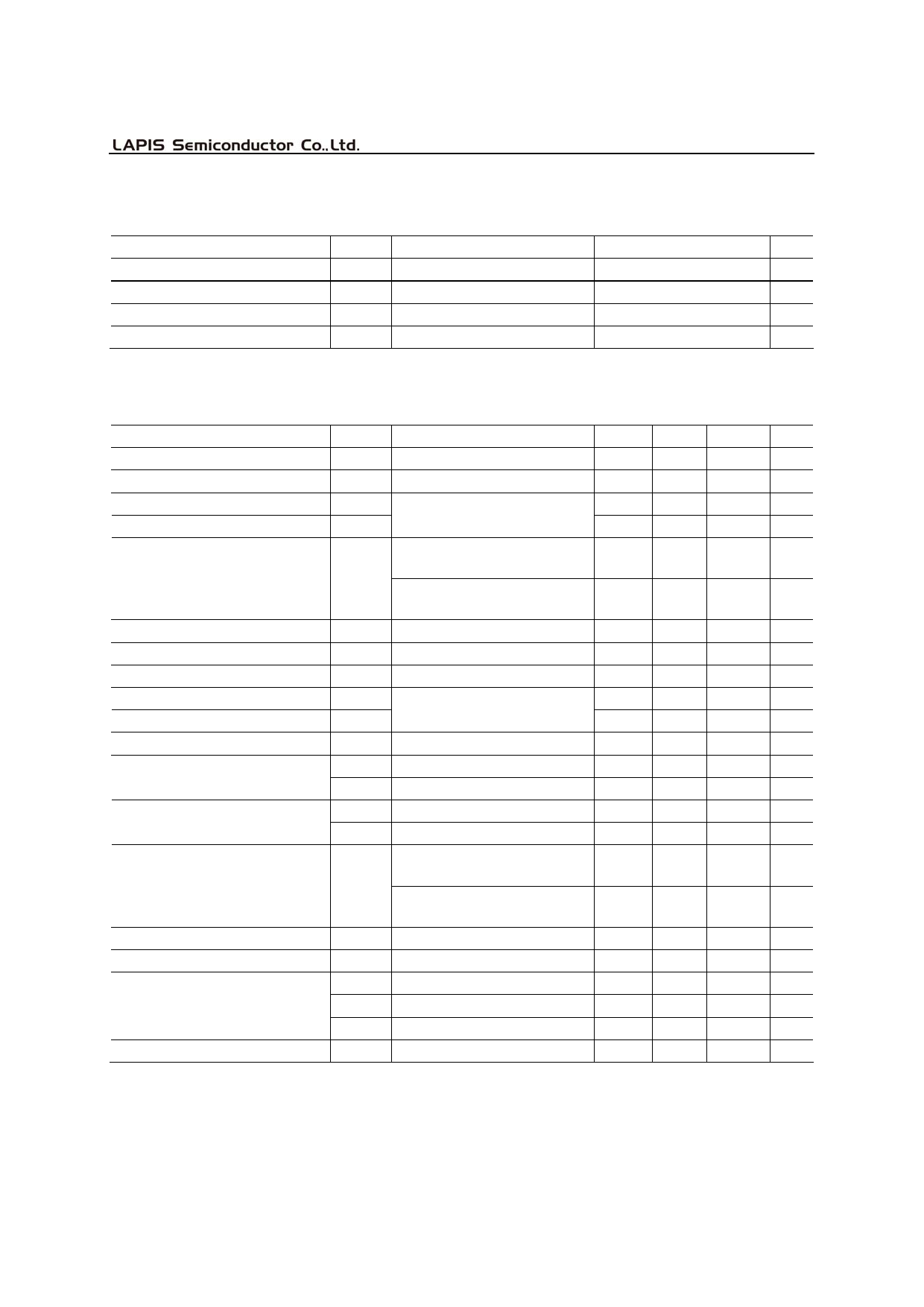

ABSOLUTE MAXIMUM RATINGS

Parameter

Power Supply Voltage

Analog Input Voltage

Digital Input Voltage

Storage Temperature

Symbol

VDD

VAIN

VDIN

TSTG

Condition

VDDD, VDDA

—

—

—

Rating

Unit

–0.3 to +7.0

V

–0.3 to VDD+0.3

V

–0.3 to VDD+0.3

V

–55 to +150

C

RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Condition

Min. Typ. Max. Unit

Power Supply Voltage

Operating Temperature

VDD Voltage to be fixed; VDDD, VDDA 4.75

5.0

TOP

—

–40

—

5.25 V

+85 C

High Level Input Voltage

Low Level Input Voltage

VIH

All digital input pins

2.2

—

VDD

V

VIL

0

—

0.8

V

MCK Frequency

FMCK

MCK = 2.048 MHz

MCKSEL (CR0-B5) bit = “0”

MCK = 4.096 MHz

MCKSEL (CR0-B5) bit = “1”

–0.01% 2048

–0.01% 4096

+0.01% kHz

+0.01% kHz

BCLK Frequency

FBCLK

BCLK

256

—

4096 kHz

Sync Pulse Frequency

FSYNC

XSYNC, RSYNC

–0.01% 8 +0.01% kHz

Clock Duty Ratio

DCLK

MCK,BCLK

40

50

60

%

Digital Input Rise Time

Digital Input Fall Time

tIR

All digital input pins

—

—

50

ns

tIF

—

—

50

ns

MCK to BCLK Phase Difference

tMB

MCK, BCLK

—

—

50

ns

Transmit Sync Pulse Setting Time tXS

tSX

BCLK to XSYNC

XSYNC to BCLK

50

—

50

—

—

ns

—

ns

Receive Sync Pulse Setting Time

tRS

tSR

Sync Pulse Width

tWS

BCLK to RSYNC

50

—

—

ns

RSYNC to BCLK

50

—

—

ns

XSYNC, RSYNC

SHORT (CR0-B4) bit = “0”

1 BCLK

—

125 s

–1BCLK

s

XSYNC, RSYNC

SHORT (CR0-B4) bit = “0”

210

— 1BCLK ns

PCMOUT Set-up Time

tDS

PCMOUT

50

—

—

ns

PCMOUT Hold Time

Digital Output Load

tDH

PCMOUT

50

—

RDL

Pull-up Resistor, PCMOUT

0.5

—

CDL1

PCMOUT

—

—

—

ns

—

k

50

pF

Bypass Capacitor for SGC

CDL2

CSG

Other output pins

SGC to AG

—

—

0.1

—

50

pF

—

F

7/52