XRT83L38 データシートの表示(PDF) - Exar Corporation

部品番号

コンポーネント説明

一致するリスト

XRT83L38 Datasheet PDF : 91 Pages

| |||

XRT83L38

OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.0

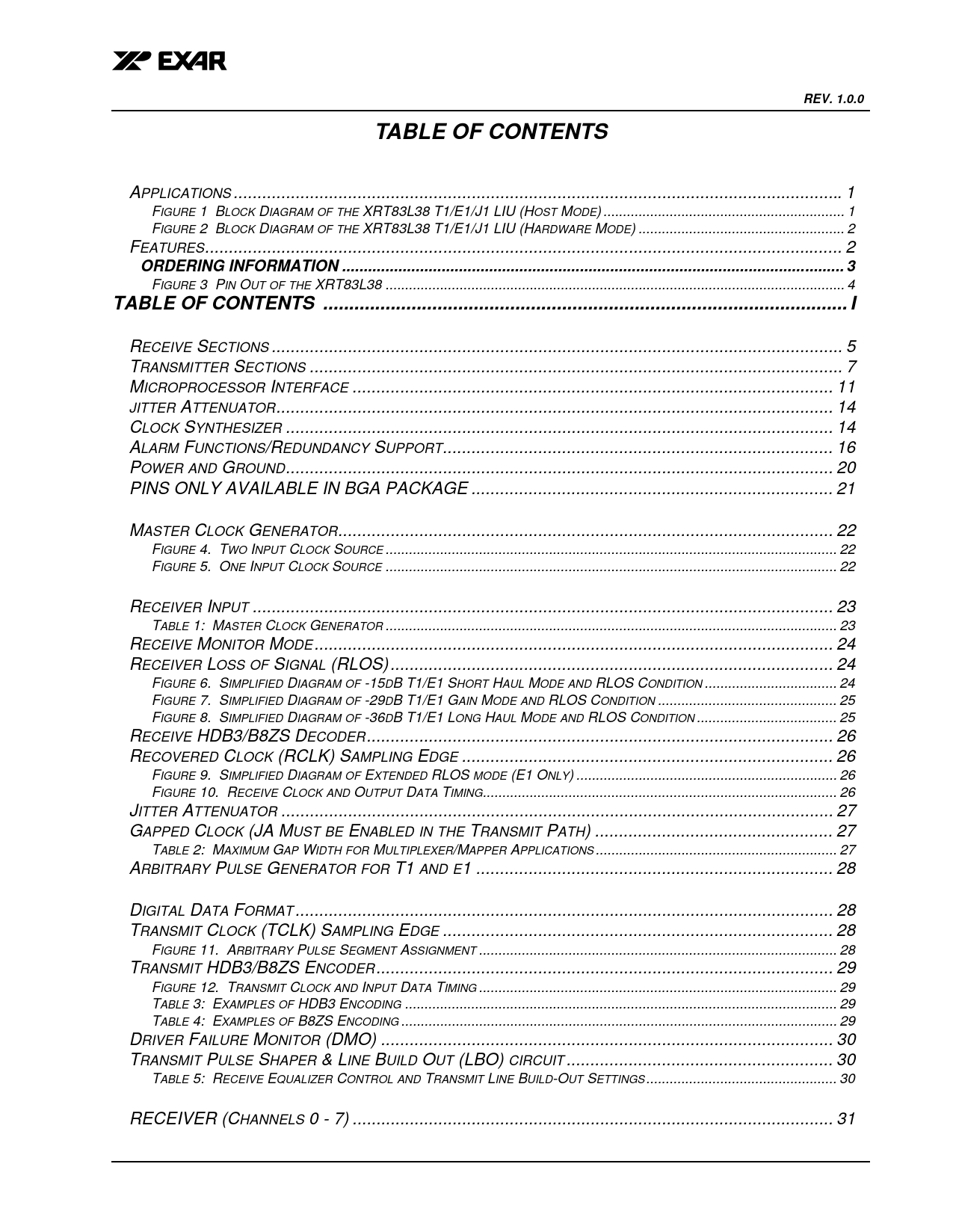

TABLE OF CONTENTS

GENERAL DESCRIPTION................................................................................................. 1

APPLICATIONS ................................................................................................................................ 1

FIGURE 1 BLOCK DIAGRAM OF THE XRT83L38 T1/E1/J1 LIU (HOST MODE) .............................................................. 1

FIGURE 2 BLOCK DIAGRAM OF THE XRT83L38 T1/E1/J1 LIU (HARDWARE MODE) ..................................................... 2

FEATURES...................................................................................................................................... 2

ORDERING INFORMATION .................................................................................................................... 3

FIGURE 3 PIN OUT OF THE XRT83L38 ...................................................................................................................... 4

TABLE OF CONTENTS ..................................................................................................... I

PIN DESCRIPTION BY FUNCTION................................................................................... 5

RECEIVE SECTIONS ........................................................................................................................ 5

TRANSMITTER SECTIONS ................................................................................................................ 7

MICROPROCESSOR INTERFACE ..................................................................................................... 11

JITTER ATTENUATOR..................................................................................................................... 14

CLOCK SYNTHESIZER ................................................................................................................... 14

ALARM FUNCTIONS/REDUNDANCY SUPPORT.................................................................................. 16

POWER AND GROUND................................................................................................................... 20

PINS ONLY AVAILABLE IN BGA PACKAGE ............................................................................ 21

FUNCTIONAL DESCRIPTION ......................................................................................... 22

MASTER CLOCK GENERATOR........................................................................................................ 22

FIGURE 4. TWO INPUT CLOCK SOURCE .................................................................................................................... 22

FIGURE 5. ONE INPUT CLOCK SOURCE .................................................................................................................... 22

RECEIVER........................................................................................................................ 23

RECEIVER INPUT .......................................................................................................................... 23

TABLE 1: MASTER CLOCK GENERATOR .................................................................................................................... 23

RECEIVE MONITOR MODE............................................................................................................. 24

RECEIVER LOSS OF SIGNAL (RLOS) ............................................................................................. 24

FIGURE 6. SIMPLIFIED DIAGRAM OF -15DB T1/E1 SHORT HAUL MODE AND RLOS CONDITION .................................. 24

FIGURE 7. SIMPLIFIED DIAGRAM OF -29DB T1/E1 GAIN MODE AND RLOS CONDITION .............................................. 25

FIGURE 8. SIMPLIFIED DIAGRAM OF -36DB T1/E1 LONG HAUL MODE AND RLOS CONDITION .................................... 25

RECEIVE HDB3/B8ZS DECODER.................................................................................................. 26

RECOVERED CLOCK (RCLK) SAMPLING EDGE .............................................................................. 26

FIGURE 9. SIMPLIFIED DIAGRAM OF EXTENDED RLOS MODE (E1 ONLY) ................................................................... 26

FIGURE 10. RECEIVE CLOCK AND OUTPUT DATA TIMING........................................................................................... 26

JITTER ATTENUATOR .................................................................................................................... 27

GAPPED CLOCK (JA MUST BE ENABLED IN THE TRANSMIT PATH) .................................................. 27

TABLE 2: MAXIMUM GAP WIDTH FOR MULTIPLEXER/MAPPER APPLICATIONS .............................................................. 27

ARBITRARY PULSE GENERATOR FOR T1 AND E1 ........................................................................... 28

TRANSMITTER ................................................................................................................ 28

DIGITAL DATA FORMAT ................................................................................................................. 28

TRANSMIT CLOCK (TCLK) SAMPLING EDGE .................................................................................. 28

FIGURE 11. ARBITRARY PULSE SEGMENT ASSIGNMENT ............................................................................................ 28

TRANSMIT HDB3/B8ZS ENCODER................................................................................................ 29

FIGURE 12. TRANSMIT CLOCK AND INPUT DATA TIMING ............................................................................................ 29

TABLE 3: EXAMPLES OF HDB3 ENCODING ............................................................................................................... 29

TABLE 4: EXAMPLES OF B8ZS ENCODING ................................................................................................................ 29

DRIVER FAILURE MONITOR (DMO) ............................................................................................... 30

TRANSMIT PULSE SHAPER & LINE BUILD OUT (LBO) CIRCUIT ........................................................ 30

TABLE 5: RECEIVE EQUALIZER CONTROL AND TRANSMIT LINE BUILD-OUT SETTINGS................................................. 30

TRANSMIT AND RECEIVE TERMINATIONS ................................................................. 31

RECEIVER (CHANNELS 0 - 7) ..................................................................................................... 31

I