IDT7188L(1996) データシートの表示(PDF) - Integrated Device Technology

部品番号

コンポーネント説明

一致するリスト

IDT7188L Datasheet PDF : 7 Pages

| |||

IDT7188S/L

CMOS STATIC RAM 64K (16K x 4-BIT)

MILITARY TEMPERATURE RANGE

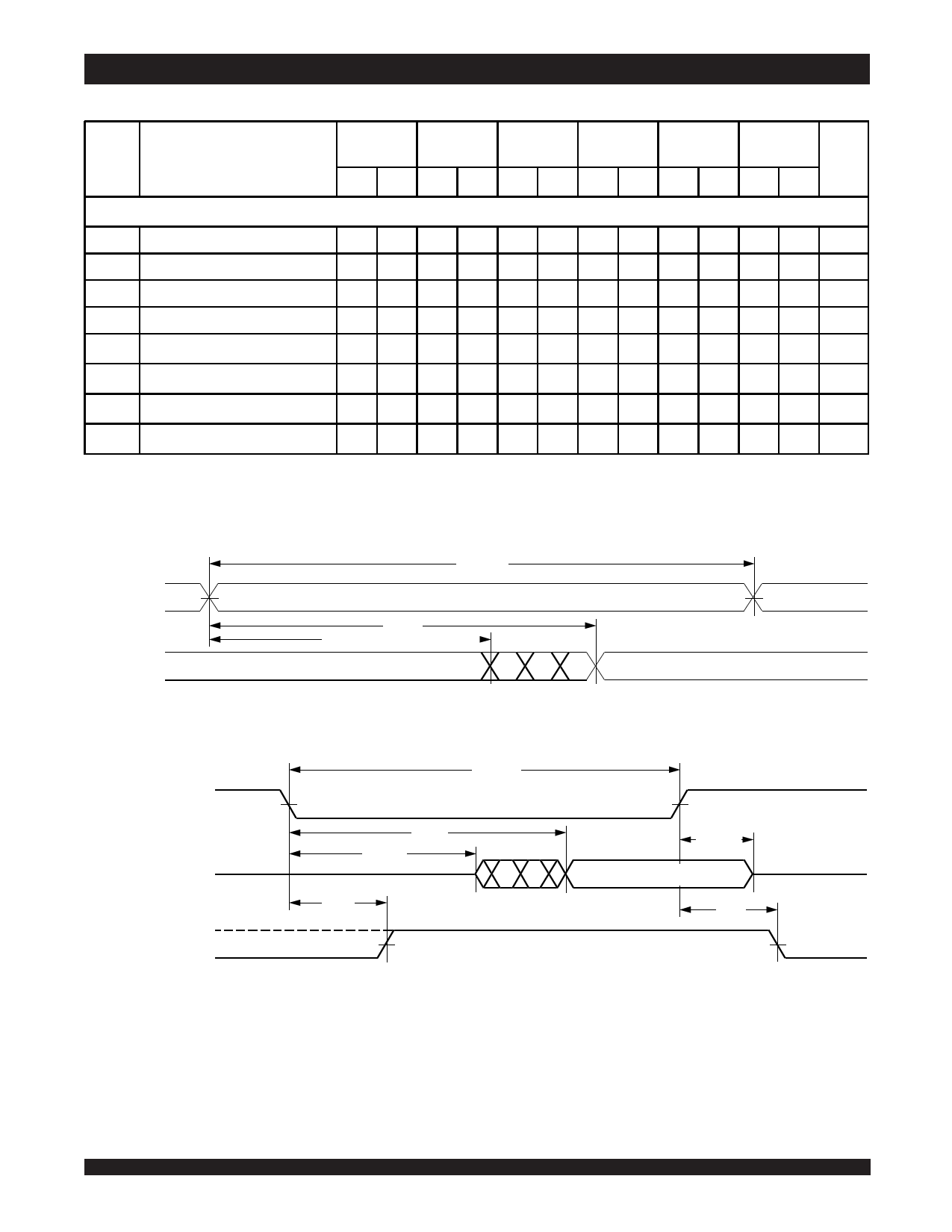

AC ELECTRICAL CHARACTERISTICS (VCC = 5.0V ± 10%, All Temperature Ranges)

Symbol

Parameter

7188S25

7188L25

7188S35/45 7188S55/70

7188L35/45 7188L55/70

7188S85

7188L85

Min. Max. Min. Max. Min. Max. Min. Max. Unit

Read Cycle

tRC

Read Cycle Time

25 — 35/45 — 55/70 — 85 — ns

tAA

Address Access Time

— 25 — 35/45 — 55/70 — 85 ns

tACS Chip Select Access Time

— 25 — 35/45 — 55/70 — 85 ns

tOH

Output Hold from Address Change

5 — 5 — 5 — 5 — ns

tLZ(1) Output Selection to Output in Low-Z

5 — 5 — 5 — 5 — ns

tHZ(1) Chip Deselect to Output in High-Z

— 10 — 14 — 20/25 — 30 ns

tPU(1) Chip Select to Power Up Time

0 — 0 — 0 — 0 — ns

tPD(1) Chip Deselect to Power Down Time

— 25 — 35/45 — 55/70 — 85 ns

NOTES:

1. This parameter is guaranteed by device characterization but is not production tested.

2989 tbl 11

TIMING WAVEFORM OF READ CYCLE NO. 1(1, 2)

tRC (5)

ADDRESS

DATAOUT

tAA

tOH

PREVIOUS DATA VALID

DATA VALID

2989 drw 06

TIMING WAVEFORM OF READ CYCLE NO. 2(1, 3)

tRC (5)

CS

DATAOUT

VCC SUPPLY ICC

CURRENT ISB

tACS

tLZ (4)

tPU

tHZ (4)

DATA VALID

tPD

NOTES:

1. WE is HIGH for Read cycle.

2. CS is LOW for Read cycle.

3. Address valid prior to or coincident with CS transition LOW.

4. Transition is measured ±200mV from steady state voltage.

5. All Read cycle timings are referenced from the last valid address to the first transitioning address.

HIGH IMPEDANCE

2989 drw 07

6.3

5