AN4506 データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

一致するリスト

AN4506 Datasheet PDF : 47 Pages

| |||

Interrupt generation

AN4506

5.1

Interrupt pin configuration

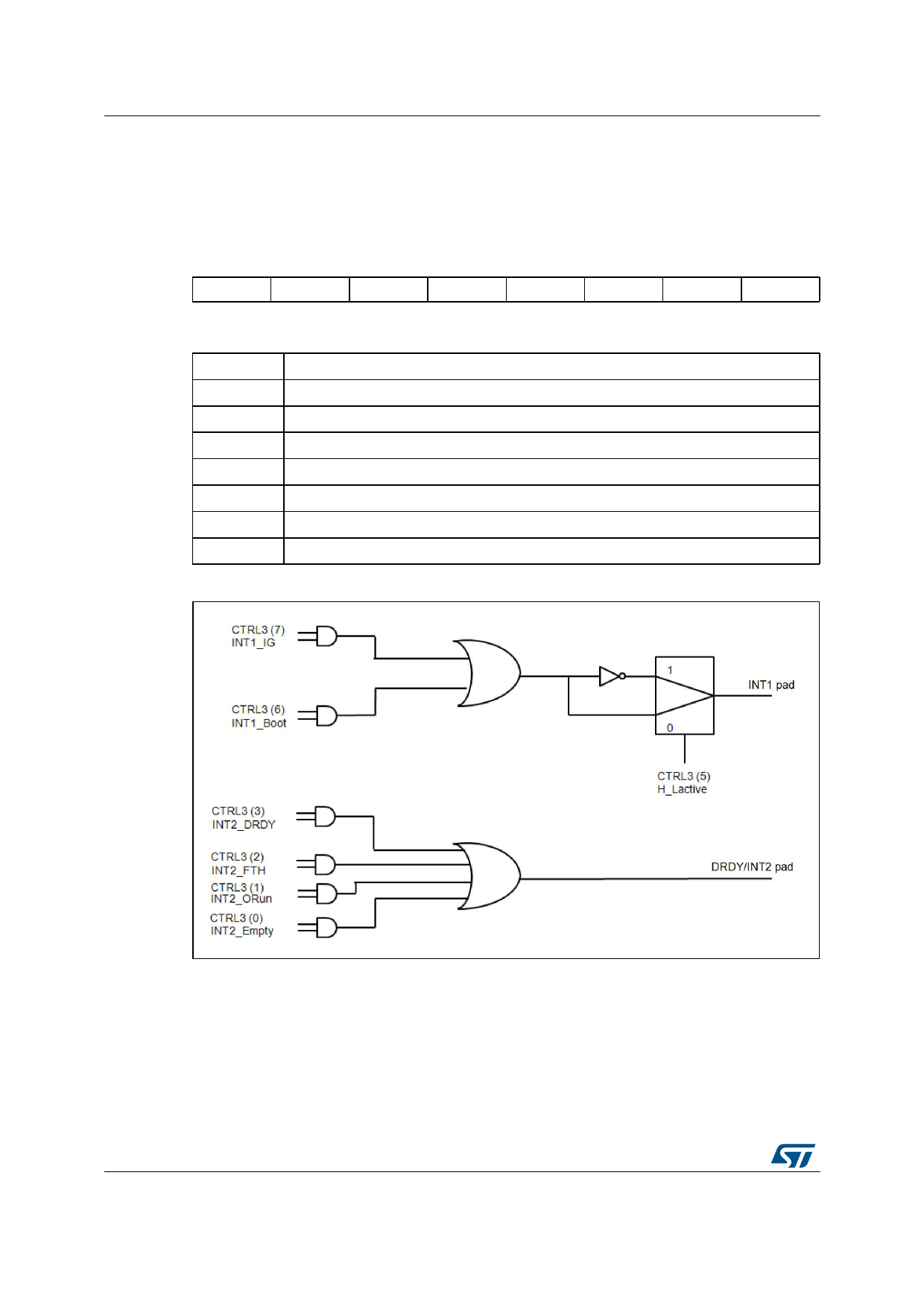

The device is provided with two pins which can be activated to generate either the data-

ready or the interrupt signals. The functionality of the pins is selected through CTRL3(22h).

Refer to Table 16, Table 17 and to the block diagram in Figure 11 for more details.

INT1_IG

Table 16. CTRL3 register

INT1_Boot H_Lactive

PP_OD INT2_DRDY INT2_FTH INT2_ORun INT2_Empty

Table 17. CTRL3 description

INT1_IG

Interrupt enable on INT1 pin. Default value 0. (0: disable; 1: enable)

INT1_Boot Boot status available on INT1. Default value 0. (0: disable; 1: enable)

H_Lactive Interrupt active configuration on INT1. Default value 0. (0: high; 1: low)

PP_OD

Push-Pull / Open drain. Default value: 0. (0: push-pull; 1: open drain)

INT2_DRDY Data Ready on DRDY/INT2. Default value 0. (0: disable; 1: enable)

INT2_FTH FIFO Threshold interrupt on DRDY/INT2. Default value: 0. (0: disable; 1: enable)

INT2_ORun FIFO Overrun interrupt on DRDY/INT2 Default value: 0. (0: disable; 1: enable)

INT2_Empty FIFO Empty interrupt on DRDY/INT2. Default value: 0. (0: disable; 1: enable)

Figure 11. Interrupt signals and interrupt pins

22/47

DocID026442 Rev 2