M65850FP データシートの表示(PDF) - Renesas Electronics

部品番号

コンポーネント説明

一致するリスト

M65850FP Datasheet PDF : 12 Pages

| |||

M65850P/FP

Function Description

1. Delay time Td

The delay time can be calculated by the equation:

Td = 8N / fck (N = the number of memory bits = 20480)

When fck = 1 MHz (fs = 125 kHz), Td can be set at 164 ms.

<Reference>

The M65850P/FP adopts ADM (Adaptive Delta Modulation) system in A/D, D/A converters.

The sampling frequency can be calculated by the following equation:

fs = clock frequency / 8 (Hz)

For clock frequency (fck ) = 1MHz, the calculated sampling frequency is :

fs= 1 MHz / 8 = 125 kHz

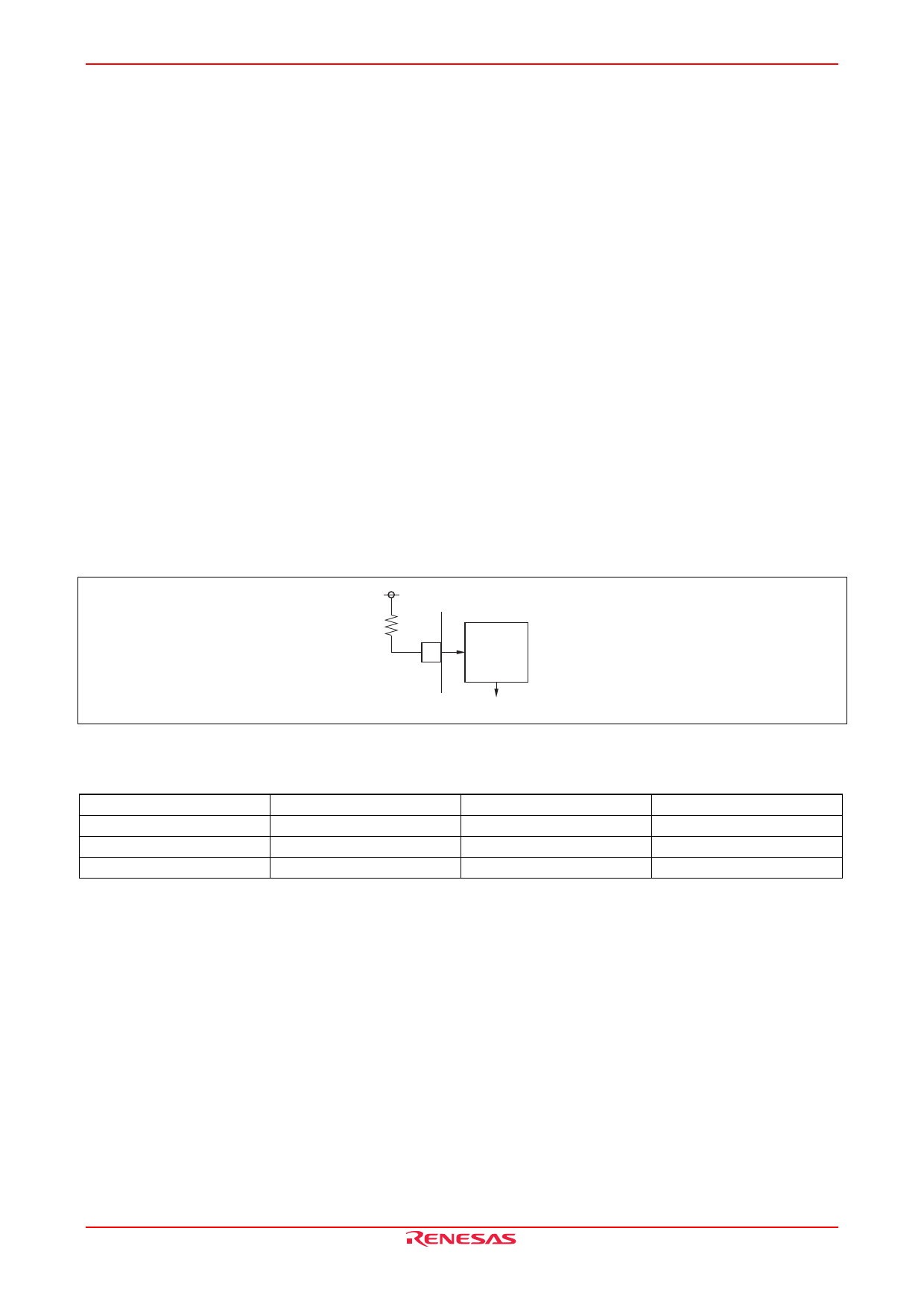

2. Clock oscillator circuit

The M65850P incorporates a current control type clock oscillator circuit in it, thus providing circuit configuration

just by connecting a resistor for current control to pin 13 (FP: pin 14) CLOCK.

Fully internal clock supply prevents occurrence of undesired radiation without affecting any external circuit.

The oscillator frequency is:

fck = 1 MHz (RC = 120 kΩ)

The resistor for current control can be calculated using the following equation.

Rc ≈ K / Clock frequency (fck) [Ω]

VCC

RC

*

13

* (FP: 14)

Clock

oscillator

circuit

Clock frequency: fck

K is the coefficient, and changes according to clock frequency, as shown below.

Delay Time (ms)

15 to 30

31 to 100

101 to 200

Clock Frequency (Hz)

11.0 M to 5.5 M

5.3 M to 1.64 M

1.62 M to 800 k

K Value

0.8 × 1011

1.0 × 1011

1.2 × 1011

(VCC = 5 V, Ta = 25°C)

RC (Ω)

7.5 k to 15 k

18 k to 62 k

75 k to 150 k

REJ03F0171-0201 Rev.2.01 Jan 25, 2008

Page 5 of 11