P4C164LL-80SM データシートの表示(PDF) - Semiconductor Corporation

部品番号

コンポーネント説明

一致するリスト

P4C164LL-80SM Datasheet PDF : 10 Pages

| |||

P4C164LL - VERY LOW POWER 8K x 8 STATIC CMOS RAM

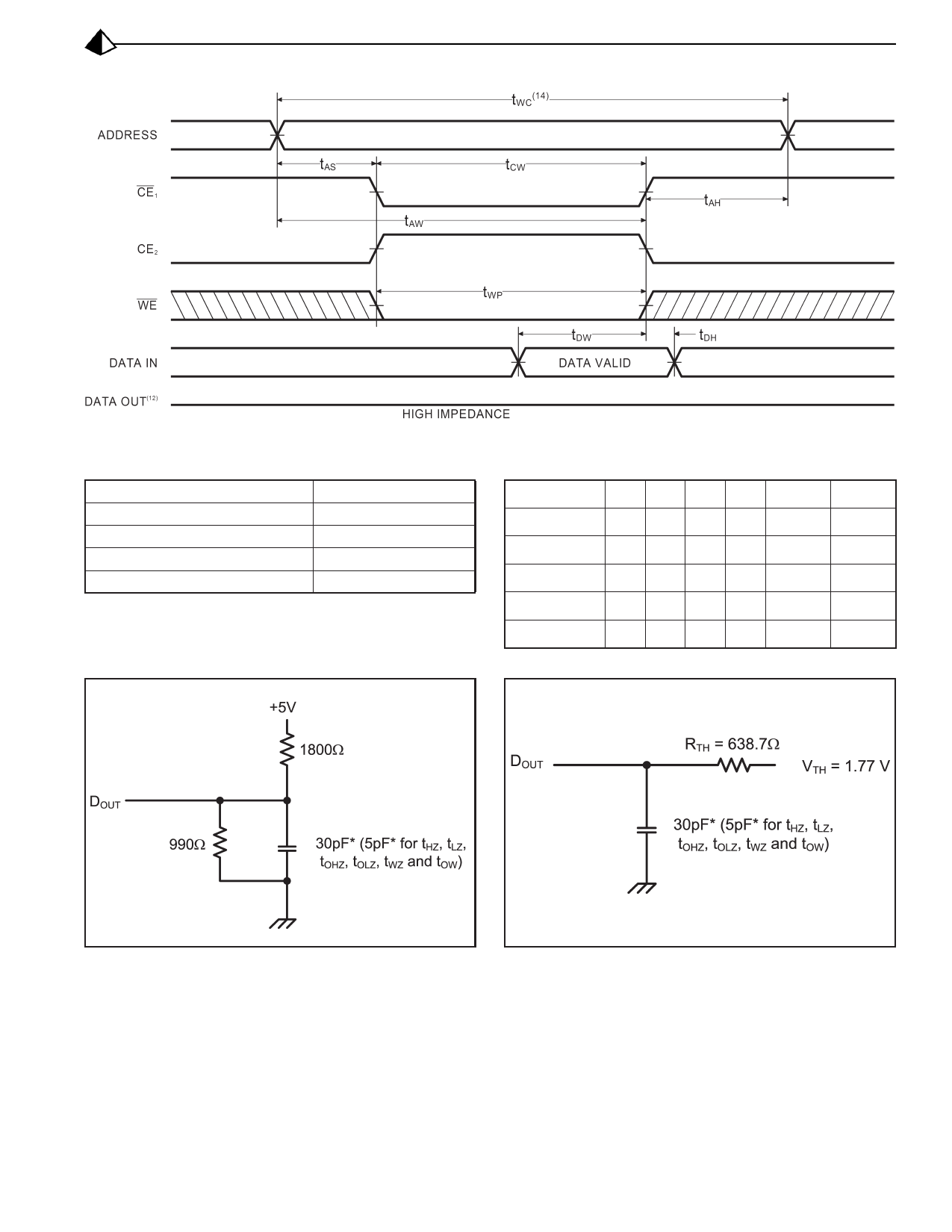

Timing Waveform of Write Cycle No. 2 (CE Controlled)(6)

AC TEST CONDITIONS

Input Pulse Levels

Input Rise and Fall Times

Input Timing Reference Level

Output Timing Reference Level

Output Load

GND to 3.0V

3ns

1.5V

1.5V

See Figures 1 and 2

TRUTH TABLE

Mode

CE1 CE2 OE WE I/O

Standby

H X X X High Z

Standby

X L X X High Z

DOUT Disabled L H H H High Z

Read

L

H

L

H DOUT

Write

L H X L High Z

Power

Standby

Standby

Active

Active

Active

Figure 1. Output Load

* including scope and test fixture.

Figure 2. Thevenin Equivalent

Note:

Because of the ultra-high speed of the P4C164LL, care must be taken

when testing this device; an inadequate setup can cause a normal function-

ing part to be rejected as faulty. Long high-inductance leads that cause

supply bounce must be avoided by bringing the VCC and ground planes

directly up to the contactor fingers. A 0.01 µF high frequency capacitor

is also required between VCC and ground. To avoid signal reflections,

proper termination must be used; for example, a 50Ω test environment

should be terminated into a 50Ω load with 1.77V (Thevenin Voltage) at

the comparator input, and a 589Ω resistor must be used in series with

DOUT to match 639Ω (Thevenin Resistance).

Document # SRAM116 REV 04

Page 6